Les contenus liés aux tags Samsung et GlobalFoundries

Afficher sous forme de : Titre | FluxPartenariat Samsung-GlobalFoundries pour le 14nm

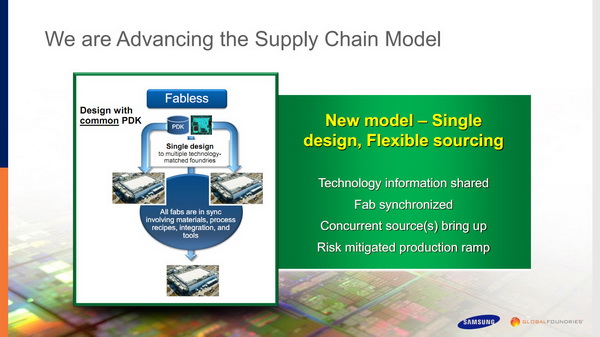

Samsung et GlobalFoundries viennent d'annoncer un nouveau partenariat stratégique autour de la technologie 14nm. Pour rappel, Samsung et GlobalFoundries sont déjà partenaires via la Common Platform , une alliance menée par IBM dans laquelle les trois entreprises partagent leurs travaux de recherche. On précisera au passage que depuis le début de l'année, une rumeur court sur la possible volonté d'IBM de se séparer de son activité « semi-conducteurs ». Un point à prendre en compte dans l'annonce sans précédent faite par les deux autres membres : un partage technologique complet autour du 14nm.

En effet, si les membres de la Common Platform utilisaient des process similaires dans les grandes lignes, dans l'implémentation ils n'étaient pas identiques. Un client souhaitant utiliser plusieurs fondeurs devant adapter son design aux particularités de chaque process. Cela change aujourd'hui avec cette annonce, quatre usines (trois appartenant à Samsung et une à GlobalFoundries) seront converties et synchronisées pour un process unique, développé principalement par Samsung, permettant aux clients d'utiliser un design unique chez ces deux fondeurs.

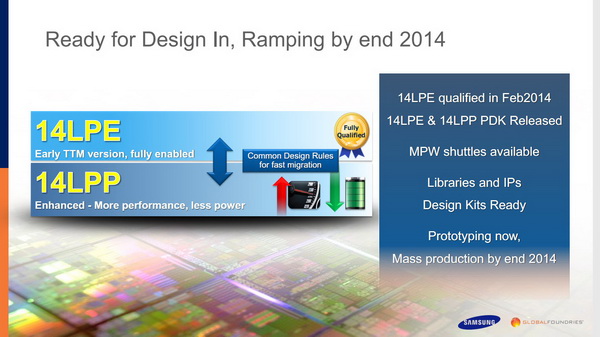

Deux versions distinctes du process 14nm seront proposées, une première baptisée LPE et pour laquelle Samsung et GlobalFoundries espèrent un début de production d'ici à la fin de l'année, et une version LPP plus optimisée sur laquelle aucun détail n'est ajouté.

Cette alliance est avant tout une aubaine pour GlobalFoundries, généralement en retard sur Samsung sur le développement de ses process, tout en étant positive pour Samsung qui permet à ses clients de disposer d'une seconde source d'approvisionnement en cas de besoin (un point de contention important pour certains de ses clients dont Apple). Obtenir de l'allocation sur les process dernier cri est généralement compliqué pour les différents acteurs du marché, certains gros clients comme Apple et Qualcomm tendant à accaparer une grande partie de l'allocation disponible. A l'heure ou Intel s'essaye aussi à entrer sur ce marché, il faudra voir si les deux sociétés arrivent à proposer - dans les temps - un partenariat qui pourrait proposer une alternative importante à TSMC, très largement numéro un du marché.

46% de parts de marché pour TSMC

IC insights a publié un résumé de l'activité en 2013 des entreprises de fabrication de semi-conducteurs ouvertes à des tiers (le concept des foundries). Dans ce marché en expansion massive (+14% en 2013) et qui représente un peu plus de 42.8 milliards de ventes au global, on retrouve deux type d'entreprises, les Pure Play et les IDM. Là où les premières ne disposent pas de produits propres - ils fabriquent uniquement pour des clients tiers - les IDM partagent leurs chaines de productions entre leurs produits et ceux de leurs clients.

Avec assez peu de surprise, TSMC écrase la concurrence avec 46.3% du marché, le second GlobalFoundries devant se contenter de 9.9%. UMC et Samsung se rapprochent également de la seconde place en étant quasi ex-aequo à 9.2%. On notera surtout que si Samsung et TSMC continuent de progresser au-delà de la moyenne de l'industrie, la croissance est un peu plus mesurée chez GlobalFoundries et UMC avec seulement 6%.

Le modèle IDM est également en passe d'être d'adopté par Intel qui annonçait en fin d'année sa volonté d'ouverture de ses usines à d'autres clients. Les ambitions du constructeur sur ce marché extrêmement concurrentiel visent avant tout les process dernier cri, là où les marges sont les plus importantes et les clients les plus volatiles. Intel a déjà signé un accord avec Altera pour la production d'un FPGA incluant un ARM 64 bits, même si Altera continue d'utiliser TSMC en parallèle. Intel souhaite pour rappel améliorer la rentabilité de ses usines qui tournent au ralenti, le constructeur ayant même annulé en janvier l'ouverture de sa Fab 42 à Chandler en Arizona. Cette fab devait pourtant être dédiée à la production de puces 14 nm que le constructeur souhaite ouvrir à des partenaires.

Focus : Common Platform Technology Forum 2013

Les acteurs de la Common Platform Alliance tenaient hier leur conférence technologique annuelle, le Common Platform Technology Forum. Pour cette sixième édition (voir notre couverture de l'édition précédente), IBM, GlobalFoundries et Samsung ont tenu a présenter quelques unes des grandes orientations technologiques pour les années a venir. Signe des temps, ARM était partenaire privilégié de la conférence et a également effectué une présentation sur laquelle nous reviendrons un peu plus...

[+] Lire la suite

Common Platform Technology Forum 2012

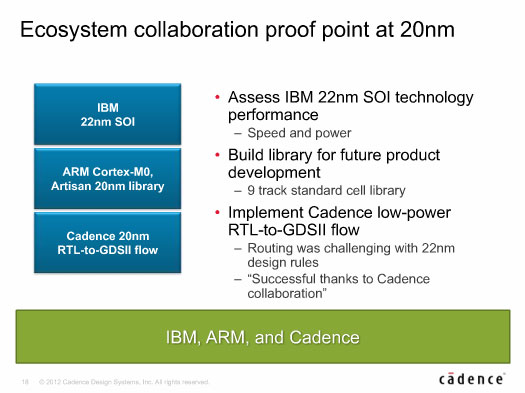

IBM, GlobalFoundries et Samsung tenaient aujourd'hui leur Technology Forum. Les trois sociétés travaillent pour rappel en commun sur le développement de leurs procédés de fabrications. Sans s'avancer réellement dans des annonces précises, les différentes sessions nous ont permis de noter quelques points intéressants.

D'abord, comme nous l'évoquions la semaine dernière, le 28nm développé par GlobalFoundries et ses autres partenaires fait l'impasse sur le SOI de type "partially-depleted" (PD-SOI), difficile à porter efficacement lorsque la finesse de gravure progresse, ce qui rend l'attrait de la technologie limitée. Si le PD-SOI est bel et bien mis au rebus (il a été confirmé qu'il ne refera pas son apparition sur le 20nm), cela ne signifie cependant pas l'arrêt total du SOI. Pour le 20nm et suivant, l'avenir selon le Dr Gary Patton d'IBM est au ETSOI. Il s'agit d'un type Fully Depleted, c'est-à-dire que le corps du transistor en lui-même qui aplani afin de contrer les effets du SOI classique. Si IBM aura mentionné plusieurs fois la présence de l'ETSOI, on notera que ce n'était pas le cas de ses partenaires qui ne se sont pas engagés précisément sur le sujet. L'allongement du délai de développement ainsi que le surcoût direct engendré sur les wafers peut en effet pousser les différents acteurs de la Common Platform à proposer, par exemple, un process avec ETSOI et un sans pour satisfaire la demande des clients. IBM aura confirmé au passage que l'ETSOI a été développé pour le 20nm en collaboration avec ST Micro.

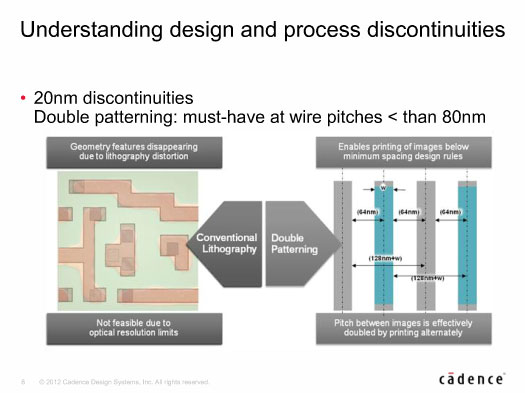

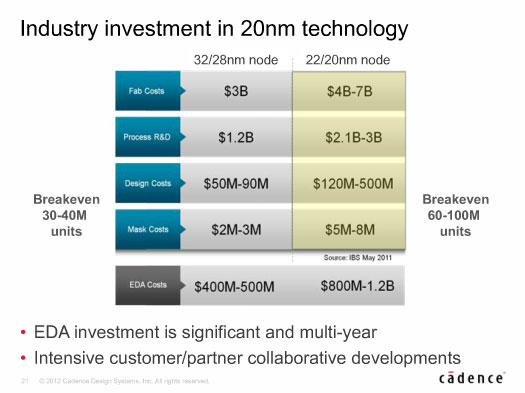

En ce qui concerne le 20nm, une annonce à tout de même été faite, celle de la nécessité du double patterning. La technologie consiste à utiliser deux expositions successives avec des masques différents pour réaliser une même couche métallique. Si toutes les couches ne sont pas concernées par la nécessité du double patterning, l'ajout des masques crée un surcoût notable. On aura noté d'ailleurs ce slide relativement édifiant sur les couts du 32/28 et du 22/20 nm :

Le surcoût sur les masques est particulièrement élevé tout comme le coût des outils de design (EDA) et du design en lui-même qui explosent en partie à cause de la complexification due au double patterning. Intel devrait lui aussi faire appel à de telles techniques pour le 16nm, cependant à notre connaissance ce n'est pas le cas pour le 22.

Autre annonce ferme, mais presque connue, l'arrivée des transistors FinFET. Pour rappel, Intel a décidé, dès le 22nm (qui arrivera sous peu avec les processeurs Ivy Bridge) de modifier la forme des transistors qui ne sont plus construits sur un plan, mais dans l'espace (voir notre focus sur le sujet pour plus de détails). Les membres de la Common Platform ont confirmé qu'il arriverait pour le 16nm, ce qui avait été sous entendu précédemment.

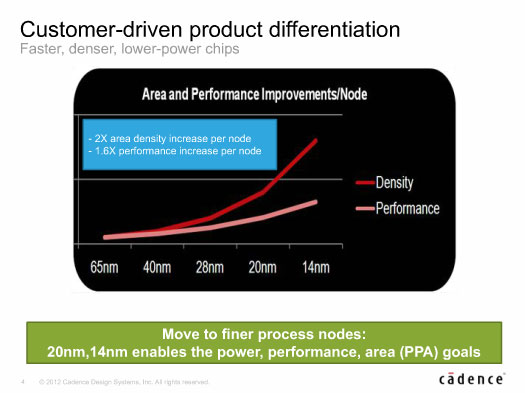

Le doublement de la densité à chaque node s'accompagne de gains de performances annoncés à 1.6x

En ce qui concerne l'au-delà du 10nm, considéré comme une barrière technologique pour les méthodes actuelles, IBM a évoqué plusieurs pistes comme l'utilisation de nanotubes de carbone. De ce côté, IBM a annoncé avoir développé de nouvelles méthodes pour trier plus facilement les nanotubes utilisables de ceux qui ne le sont pas. Gary Patton évoquait ainsi que 30% des nanotubes semi conducteurs produits étaient pleinement conducteurs et devaient donc être supprimés. En ce qui concerne la lithographie EUV, qui se fait attendre depuis plusieurs générations, il faudra encore attendre. Si IBM laissait entre ouverte une porte pour le 16nm, il est plus probable que la technologie ne soit pas à l'heure pour ce node.

Nous aurons noté enfin durant la conférence quelques petites phrases. D'abord, et à plusieurs reprises, des allusions sur le fait que les fabs 28nm de la Common Platform étaient fonctionnelles et non pas arrêtées. Un écho à un article relativement surprenant publié par nos confrères de SemiAccurate la semaine dernière qui indiquait que TSMC aurait stoppé complètement la production sur ses lignes 28nm il y a trois semaines de cela, pour un problème qui n'aurait pas été précisé. Une information difficile à vérifier et si nous avions entendu un temps des rumeurs sur d'éventuels retards de livraisons pour certains GPU produits par TSMC, elles se sont estompées depuis. La référence - multiple - à cette rumeur par les concurrents de TSMC était pour le moins originale.

On aura noté enfin, de la part de Subramani Kengeri de GlobalFoundries que si jusqu'ici la production de CPU et de GPU avait poussé en avant le développement des process de technologies, c'est aujourd'hui les SoC et les puces basse consommation qui forcent les décisions de design. AMD appréciera.

450 mm, tout le monde s'accorde !

Nos confrères d'EEtimes rapportent aujourd'hui la création de deux plans d'investissements concernant les semi conducteurs dans l'état de New York, aux Etats Unis. Le premier concerne l'alliance technologique "Common Platform" (IBM, GlobalFoundries et Samsung) qui annonce un investissement de 3.6 milliards de dollars sur le développement des process de fabrication en 22 et 14nm.

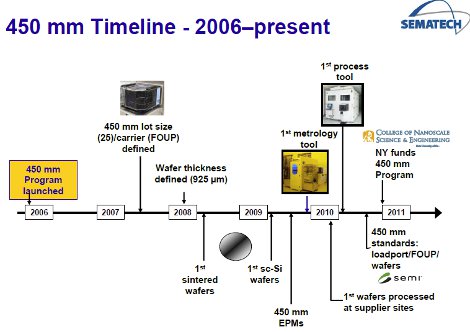

L'autre investissement est encore plus particulier puisqu'il s'agit de l'annonce du Global 450 Consortium (G450C), un regroupement de l'industrie autour de la transition vers des wafers de 450mm de diamètre (contre 300 aujourd'hui). Pour rappel, augmenter le diamètre des wafers permet de réaliser des économies d'échelle en augmentant la quantité de puces que l'on peut produire.

Cette transition de l'industrie, voulue depuis des années par Intel s'est heurtée jusqu'ici au reste de l'industrie (Intel dépend également des fabricants d'outils de photolithographie, eux-mêmes dépendant des autres fabricants de semiconducteurs), plutôt hésitante sur le sujet. Les transitions successives vers des procédés de gravures de plus en plus fins ont conduit à une diminution de la taille des puces, qui si elle est compensée chez Intel par une augmentation des transistors, ne l'est pas forcément pour tous les clients des autres fabricants.

L'investissement à New York sera réalisé en partie par Intel qui y construira un centre de recherche et de développement autour de cette technologie. L'annonce la plus importante tient aux membres annoncés du Global 450 Consortium, à savoir bien évidemment Intel, mais également les membres de la Common Platform (IBM, GlobalFoundries, Samsung) et TSMC qui investiront conjointement 575 millions de dollars sur le sujet. Les constructeurs d'outils comme ASML ont également indiqué qu'ils proposeraient sous peu des solutions 450 mm de type EUVL.

GlobalFoundries, jusqu'ici réticent sur le 450 mm a évoqué son arrivée possible pour le node 14nm. Intel de son côté n'a pas précisé de délai pour sa transition à cette technologie.