Les derniers contenus liés aux tags HMC et 3D XPoint

Alliance autour d'un nouveau bus mémoire

HMC, DDR5 et 3D XPoint pour Micron

IDF: Roadmap mémoire Micron

Alliance autour d'un nouveau bus mémoire

Plusieurs acteurs majeurs de l'industrie viennent d'annoncer une alliance dans le but de développer une nouvelle interface mémoire. Ils se sont regroupés au sein d'un consortium baptisé Gen-Z.

La page de description du consortium insiste sur un mode de fonctionnement transparent et ouvert. Le consortium en lui même est une organisation à but non lucratif (pour les puristes, une entreprise américaine de type "not for profit"). Le mode de développement sera transparent, et le standard final sera publié, disponible et utilisable gratuitement.

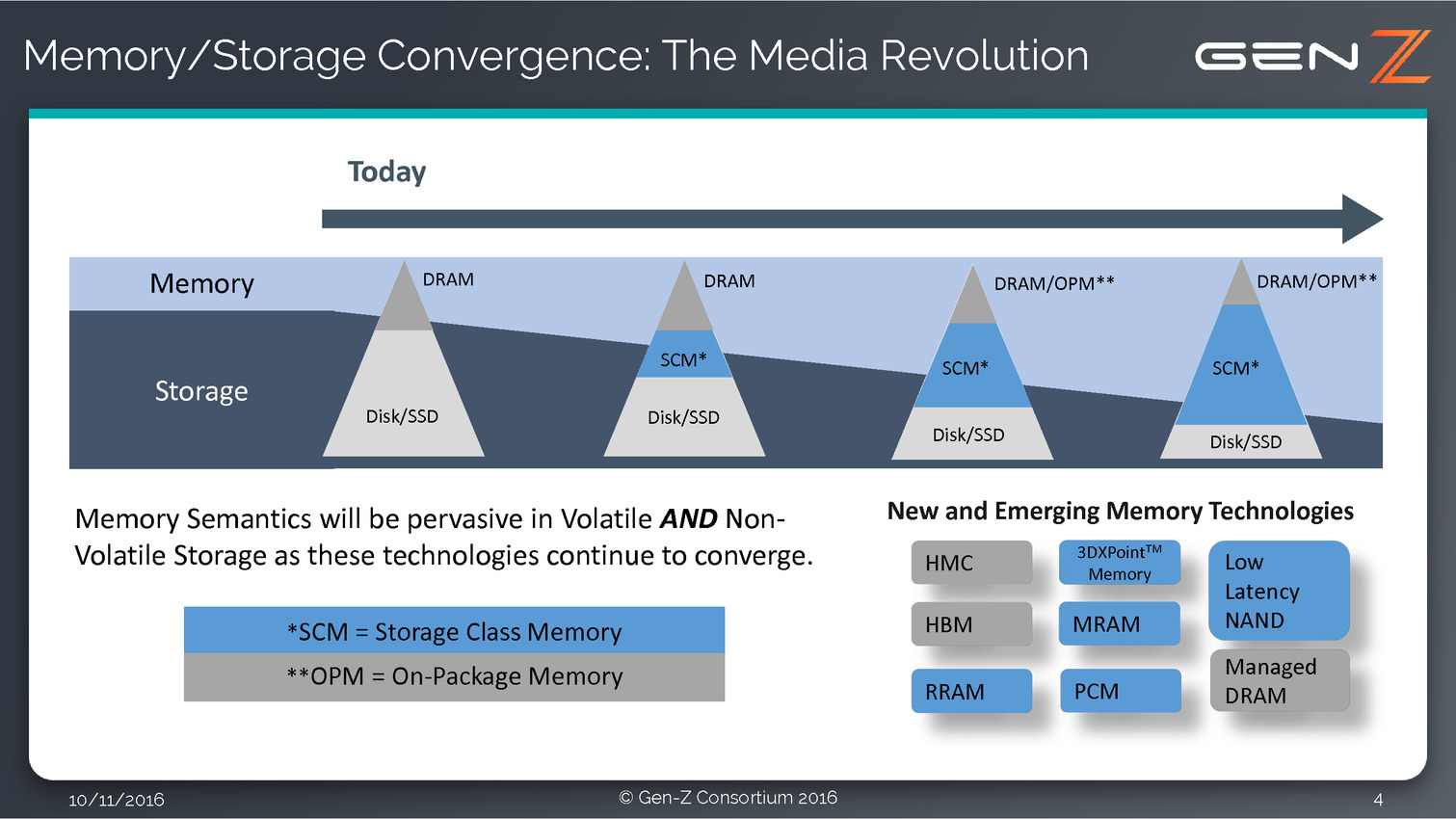

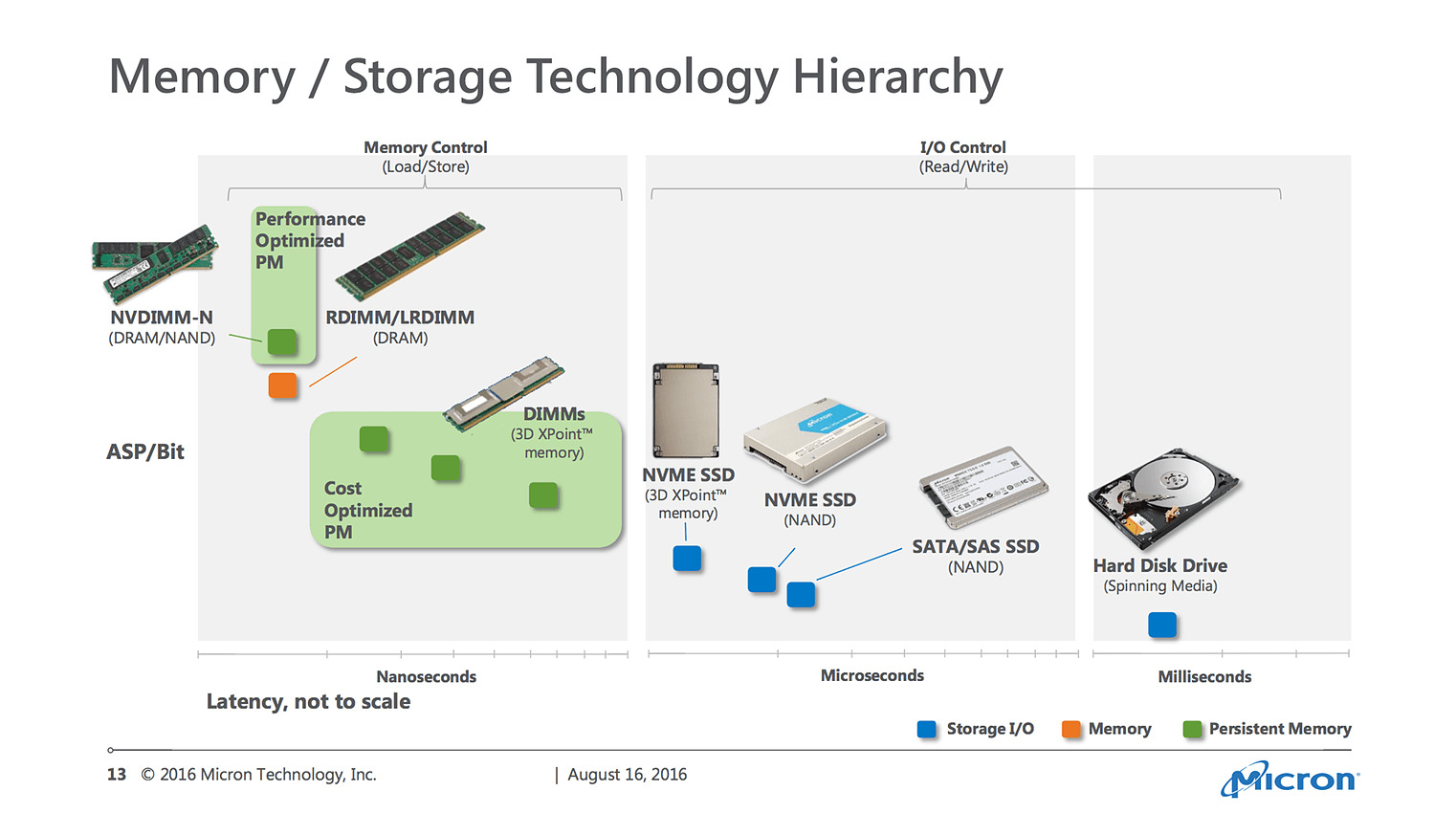

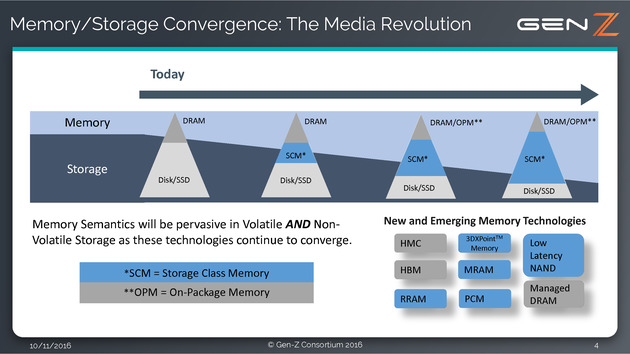

Techniquement il s'agit de proposer une nouvelle manière d'interconnecter la mémoire, ou plutôt les multiples types de mémoires qui pourront coexister à l'avenir.

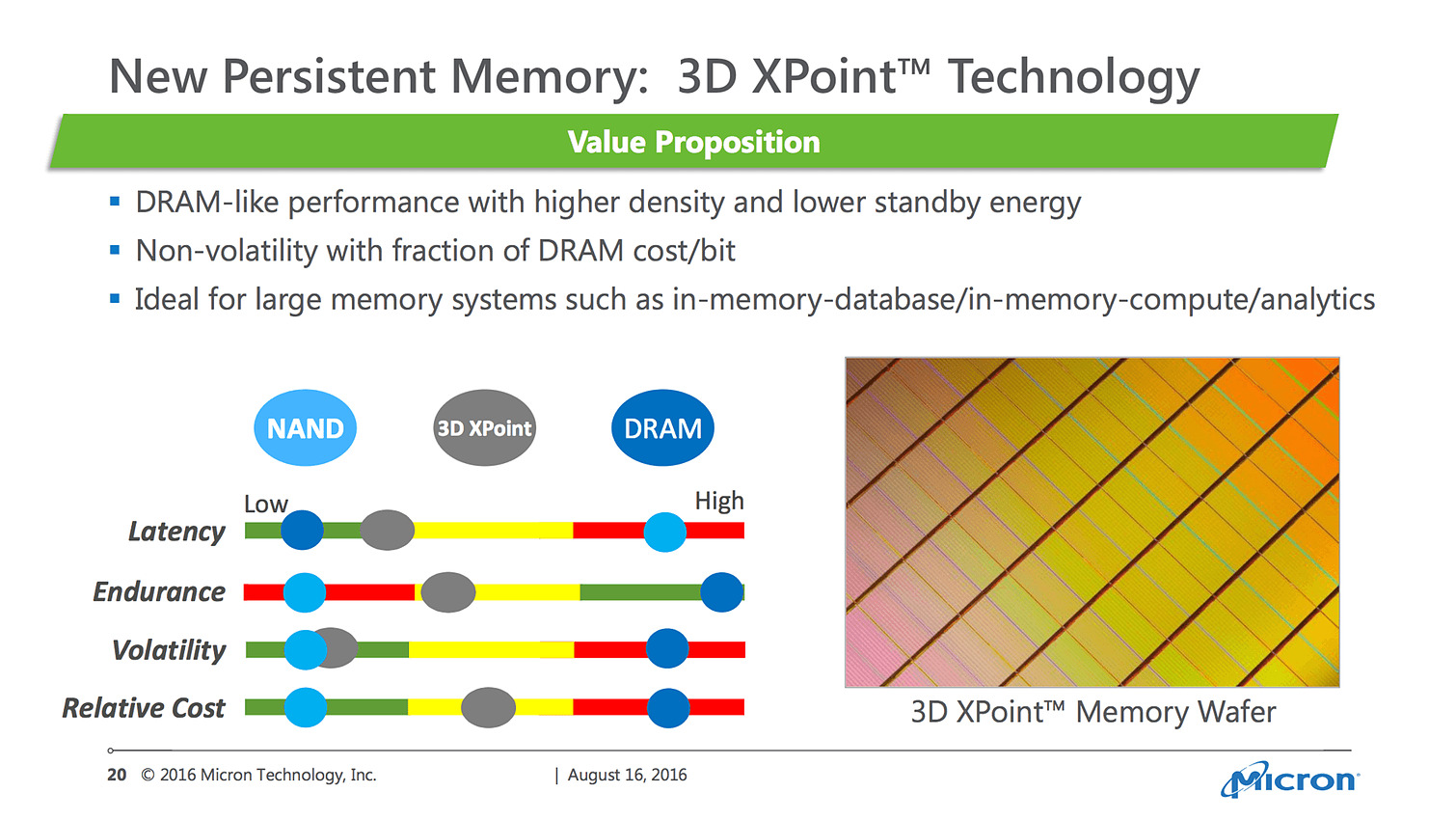

Le consortium prend l'exemple des nouveaux "types" de mémoires, appelés SCM (Storage Class Memory) comme peuvent l'être les RRAM, MRAM, ou les implémentations commerciales annoncées comme 3D XPoint chez Intel/Micron ou la Z-NAND de Samsung. Ces nouveaux types de mémoires viennent s'ajouter à la mémoire traditionnelle (DRAM) qui voit aussi arriver de nouvelles variantes (HBM ou HMC).

L'idée de base du consortium est de proposer une interface avec des commandes très simples, proches de celles utilisées pour la DRAM, mais qui puissent être utilisées aussi bien au sein d'un package, sur la carte mère, ou au delà (communication entre serveurs dans un data center). Le tout se doit de rester compatible avec l'existant, y compris les systèmes d'exploitations qui pourront exploiter ces nouvelles mémoires de manière transparente. Un but assez noble tant la question de comment adresser ce nouveau tiers de mémoire avait été évitée jusqu'ici.

Le consortium annonce qu'il utilisera entre autre le protocole IEEE 802.3 (Ethernet) comme protocole de communication interne (on pourra aussi utiliser Ethernet pour la couche physique de transport). En plus des protocoles, un nouveau connecteur devrait être annoncé pour tenter de standardiser ces futurs types de mémoire, il supportera jusque 112 GT/s.

Les objectifs fixés sont particulièrement audacieux, et on ne pourra que se féliciter de voir tant d'acteurs majeurs de l'industrie s'associer pour tenter de proposer un nouveau standard :

L'absent le plus notable est Intel, et il est difficile de ne pas voir cette alliance comme formée contre la firme de Santa Clara qui a tendance à développer ses bus de manière propriétaires, particulièrement pour tout ce qui touche au monde serveur.

Il est tout de même intéressant de voir que Micron, partenaire d'Intel sur 3D Xpoint est présent dans le consortium (3D Xpoint est même mentionné dans les slides de présentation). Il sera intéressant de suivre l'évolution de ce standard qui pourrait apporter des solutions concrètes aux problématiques d'interconnexions.

Vous pouvez retrouver la présentation du consortium ci dessous :

HMC, DDR5 et 3D XPoint pour Micron

Micron a également pris la parole pendant la première matinée de Hot Chips, comme nous le rapportent une fois de plus nos confrères de ComputerBase . Ces derniers qualifient d'une honnêteté rafraîchissante la présentation de Micron, ne cherchant pas forcément à annoncer des chiffres extravagants. La société aurait même regretté, si l'on en croit nos confrères, que son partenaire Intel ait annoncé beaucoup trop tôt la mémoire 3D XPoint !

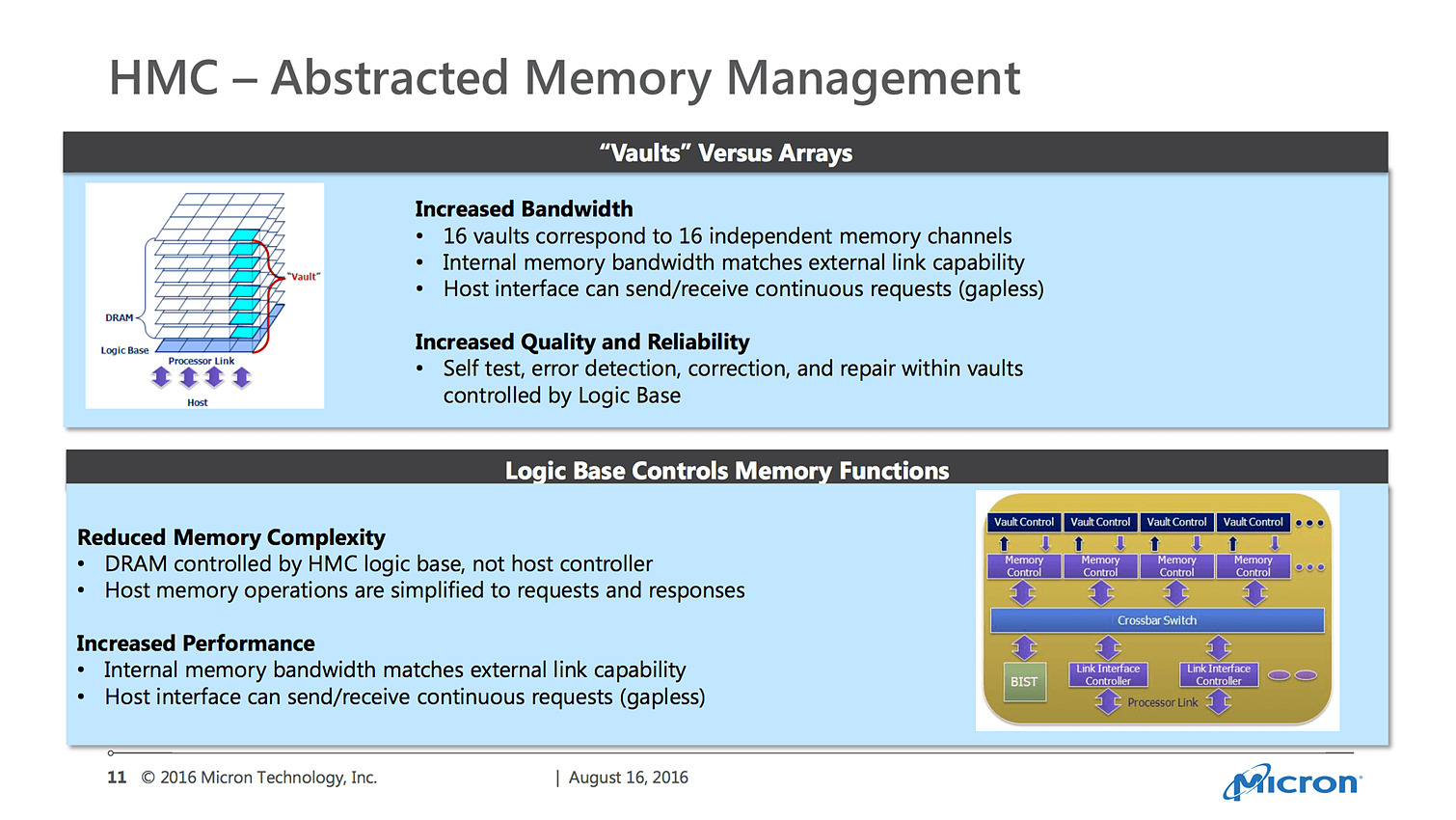

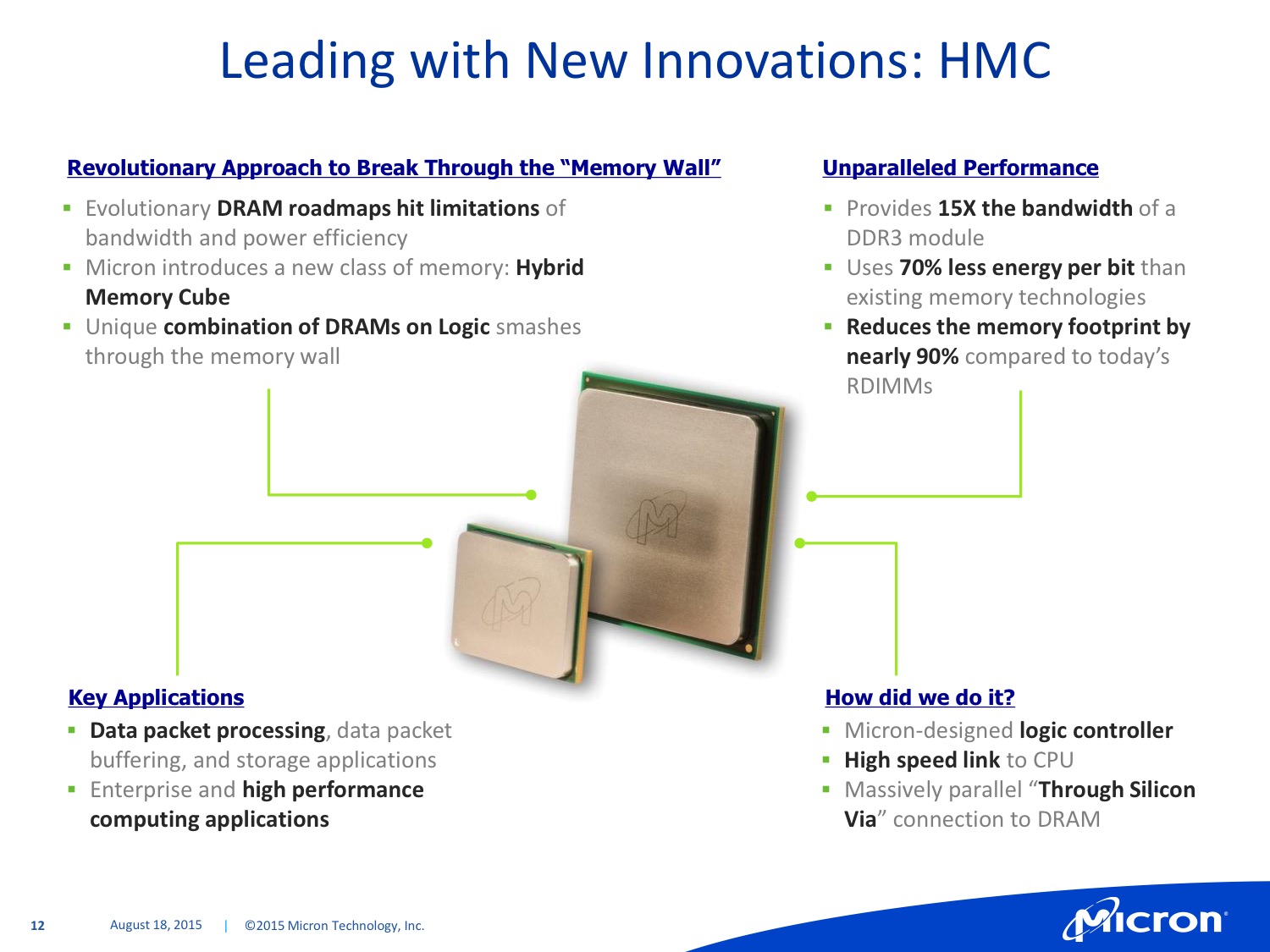

Dans le détail, Micron n'aura pas pu s'empêcher tout de même de qualifier la HBM de "mauvaise copie" de sa propre technologie Hybrid Memory Cube, plus complexe, coûteuse, et surtout assez peu disponible (elle devrait être présente sur le prochain Xeon Phi d'Intel, Knights Landing). Micron estime que la HMC dispose de nombreux avantages pour le marché du HPC, avec par exemple un meilleur algorithme de CRC que celui utilisé par le JEDEC pour la HBM.

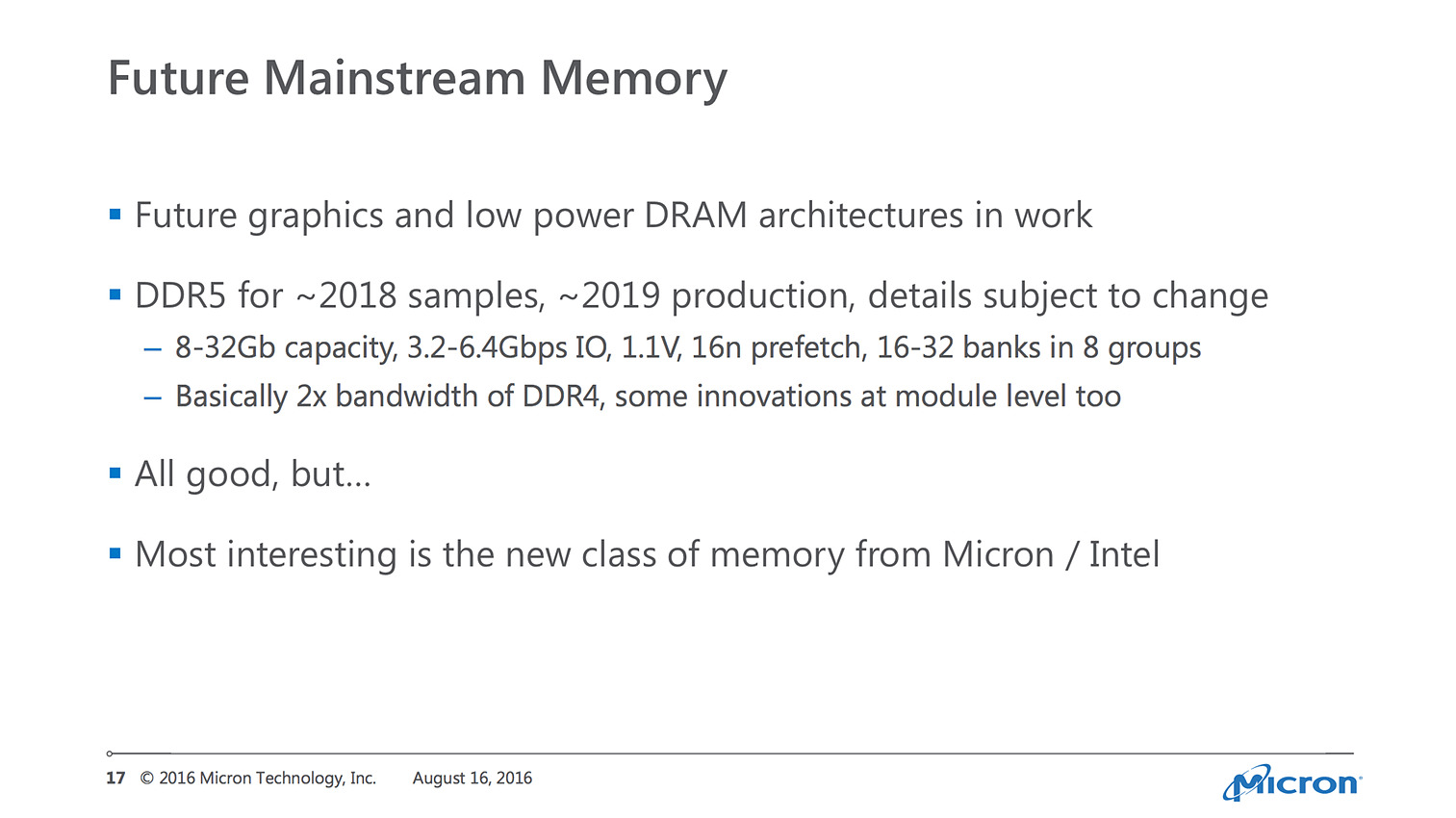

Micron aura également évoqué la DDR5 qui aura pour objectif de doubler la bande passante par rapport à la DDR4. Micron estime produire ses premiers échantillons courant 2018, avec une production en volume possiblement en 2019, mais plus probablement pour 2020.

Outre le tacle envers son partenaire Intel sur la mémoire 3D XPoint, on ne retiendra pas beaucoup d'informations, si ce n'est que Micron confirme que ce nouveau type de mémoire sera en production avant la fin de l'année.

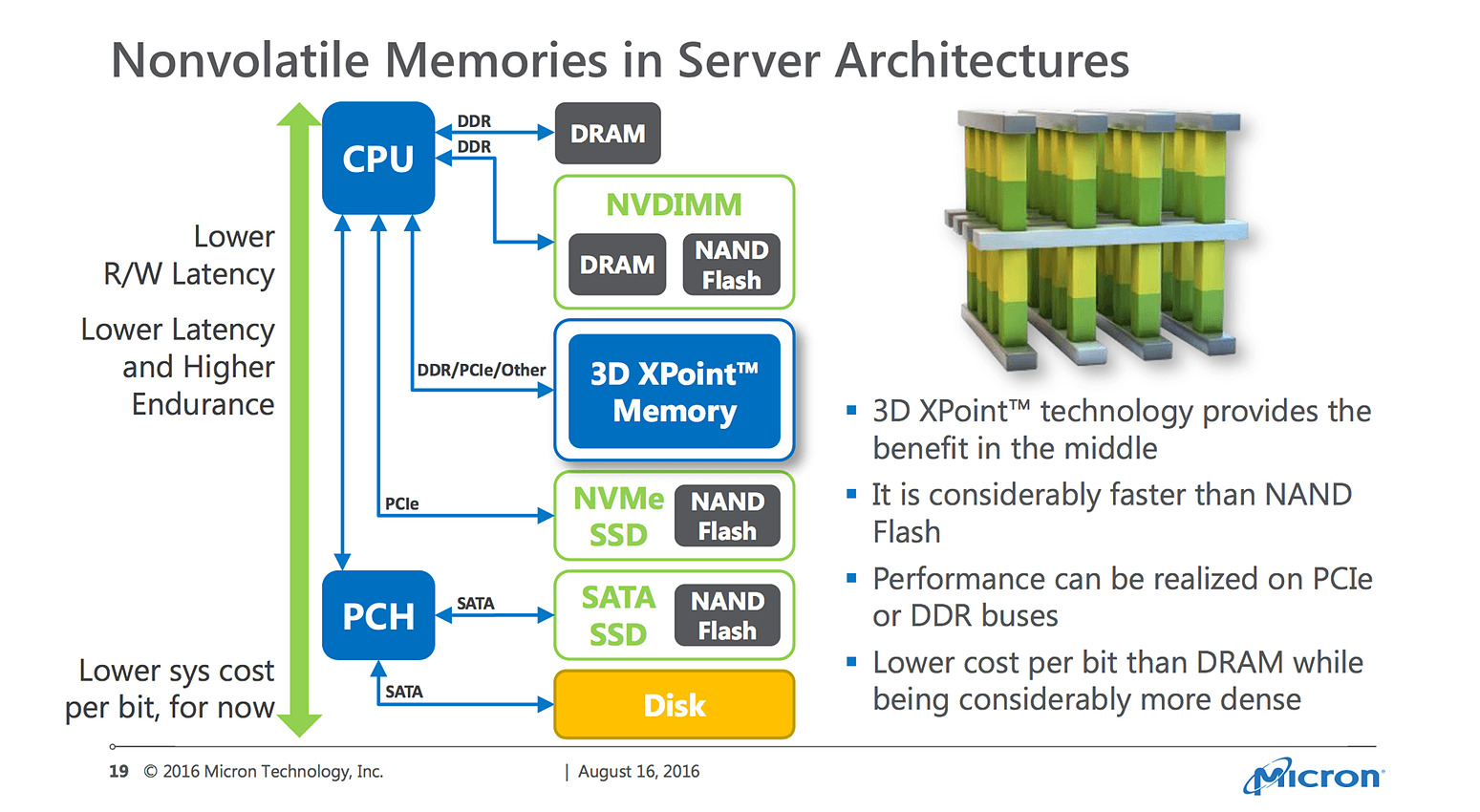

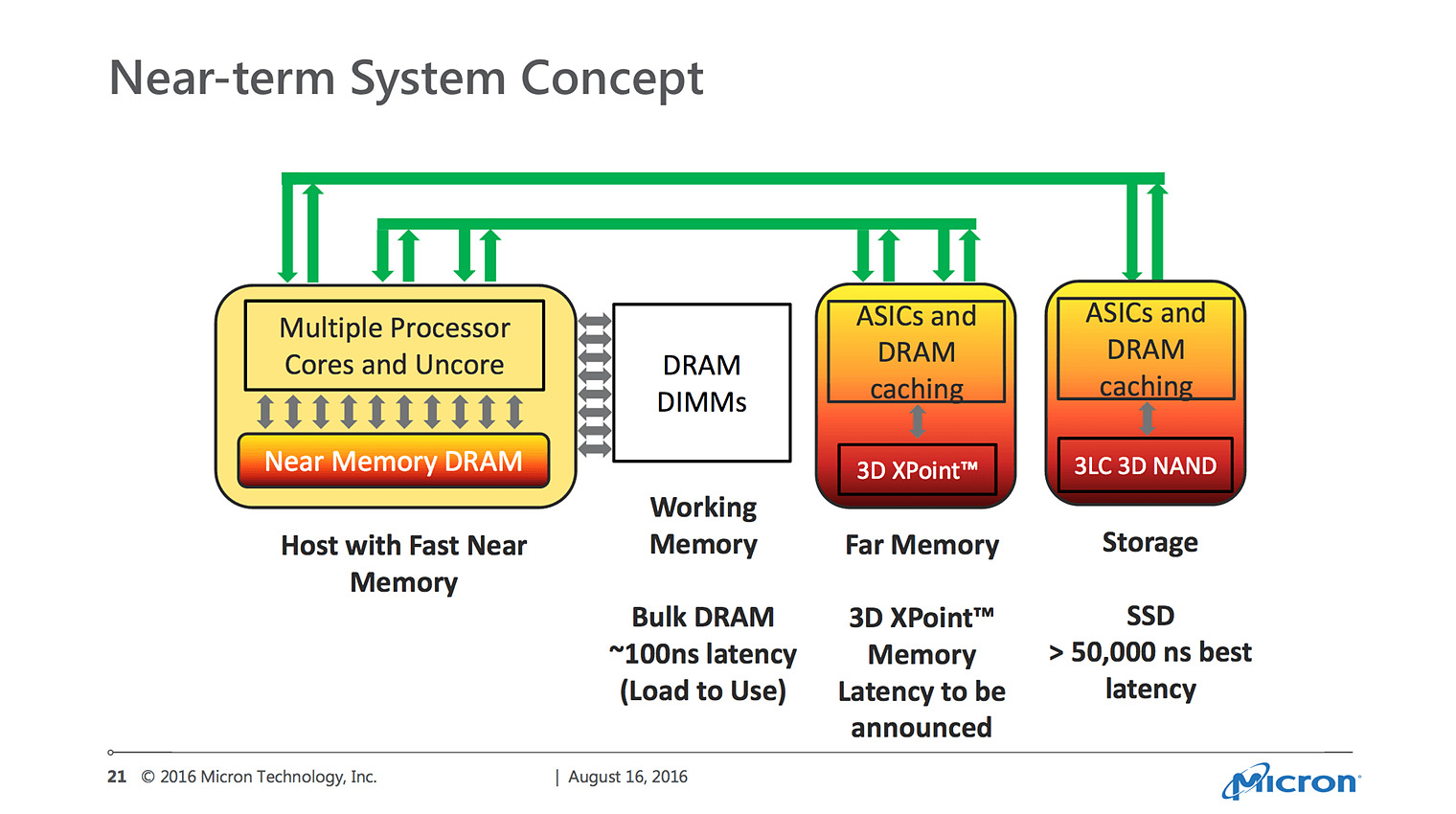

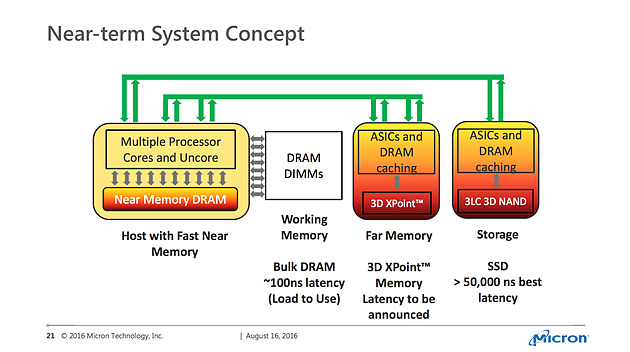

On retiendra ce dernier slide qui préfigure de ce que l'on devrait voir arriver sous peu sur les serveurs, avec deux tiers de mémoire DRAM. D'un côté une mémoire "proche", intégrée au processeur et rapide (HBM, ou plutôt HMC dans la vision de Micron) qui s'adjoint à la mémoire DRAM en barrettes plus classique. 3D XPoint et la 3D NAND proposant de leur côté deux tiers de stockages persistants.

Micron continue dans sa voie de l'originalité, dans un marché de la mémoire certes très concurrentiel. La société continue de mettre en avant sa GDDR5X, certes standardisée par le JEDEC mais qui n'a pas été adoptée par ses concurrents, mais aussi des solutions plus propriétaires comme l'Hybrid Memory Cube et 3D XPoint. Avec les ambitions de SK Hynix et de Samsung de pousser la HBM sur le terrain des PC clients, on peut cependant se demander si le pari d'ignorer la mémoire HBM ne se retournera pas contre Micron dans les mois à venir.

IDF: Roadmap mémoire Micron

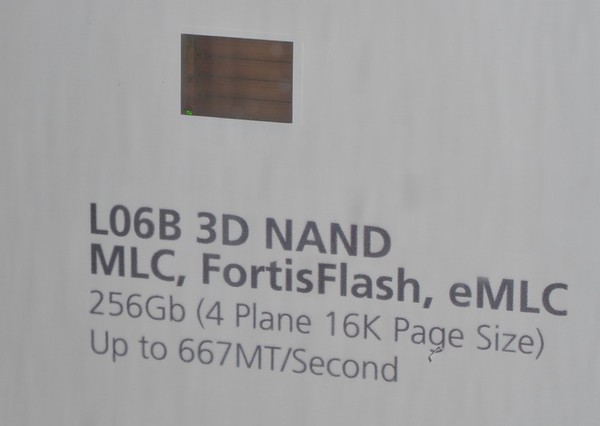

Le partenaire d'Intel sur la mémoire 3D XPoint était présent sur l'IDF avec un stand ou l'on pouvait apercevoir un wafer de NAND 16nm, ainsi qu'un module 3D NAND de 256 Gbits.

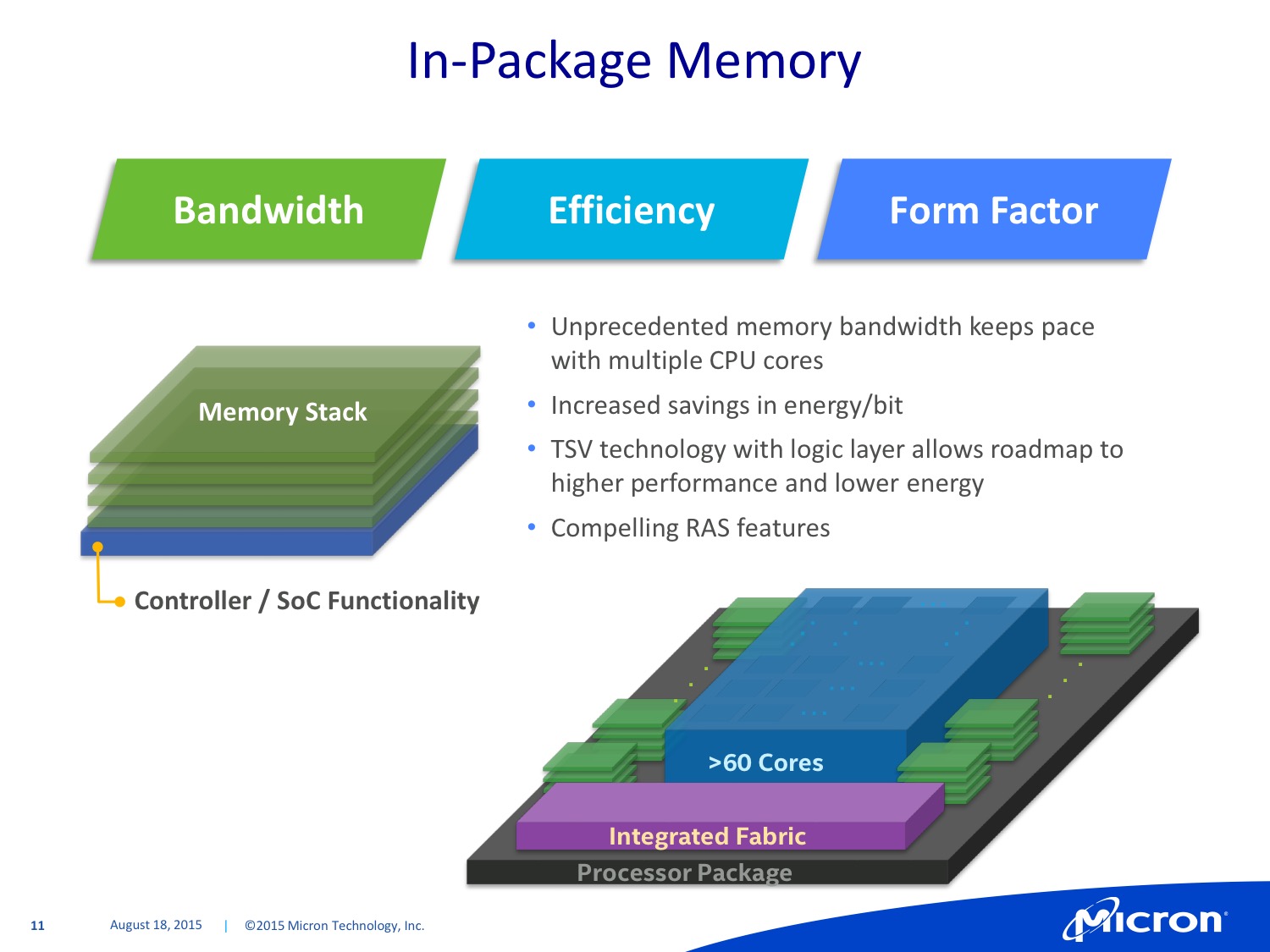

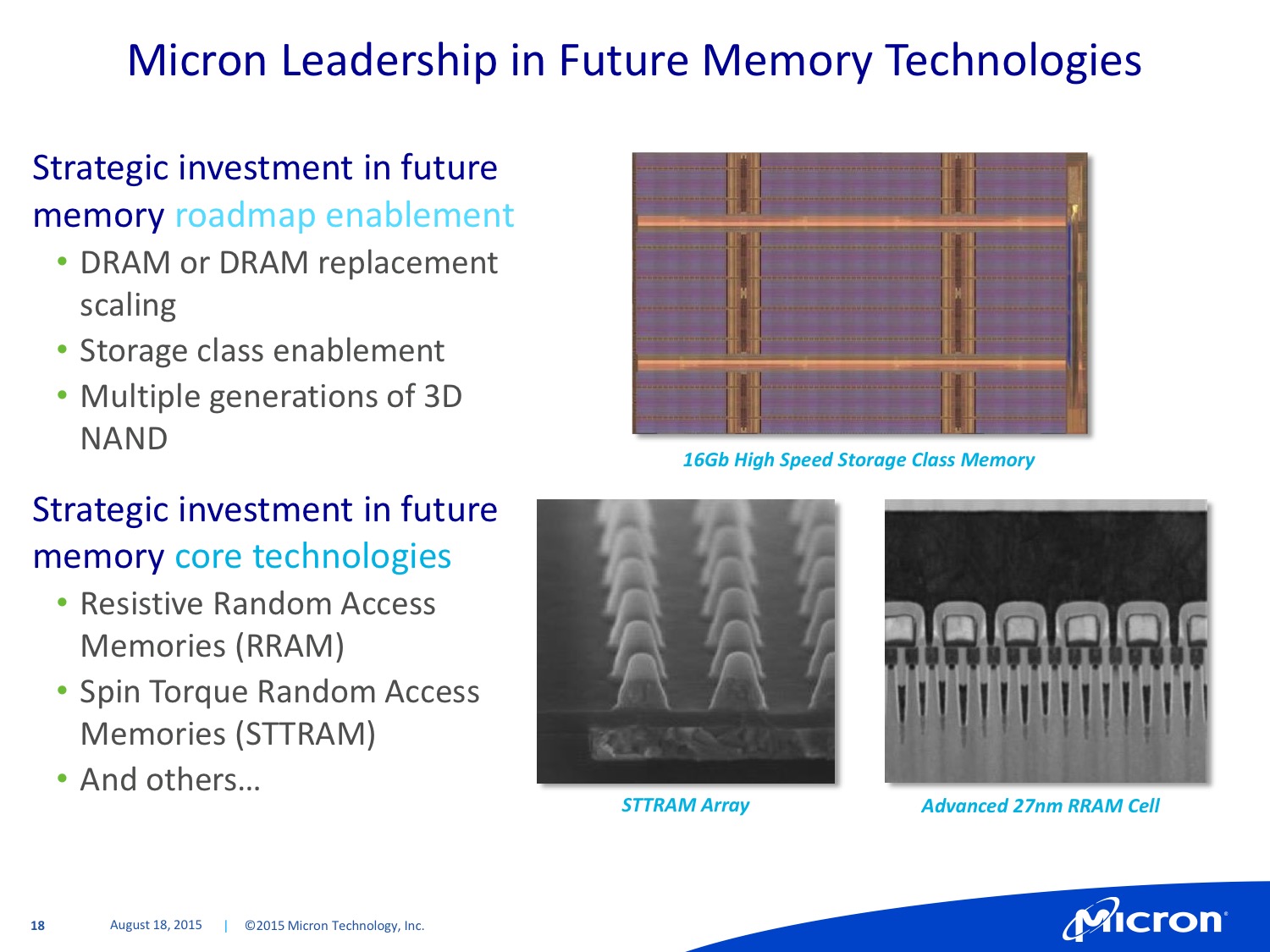

La société a également effectué une présentation ou elle a évoqué ses technologies mémoires. Le constructeur continue de travailler sur l'Hybrid Memory Cube (HMC), une technologie qui supperpose des dies de mémoires avec une couche de contrôleurs logiques. La troisième génération est en cours de développement même si l'on ne sait pas encore ce qu'elle apportera.

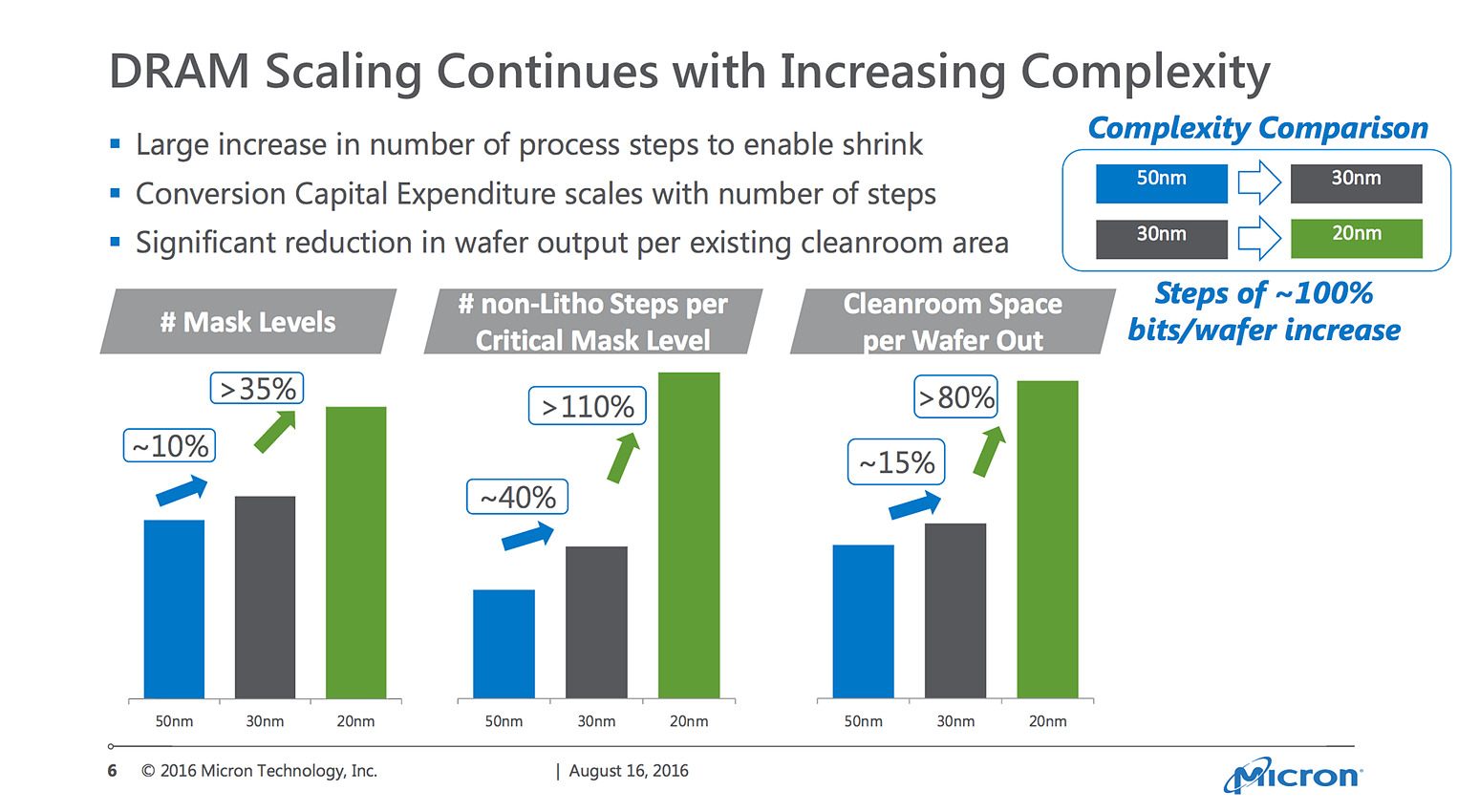

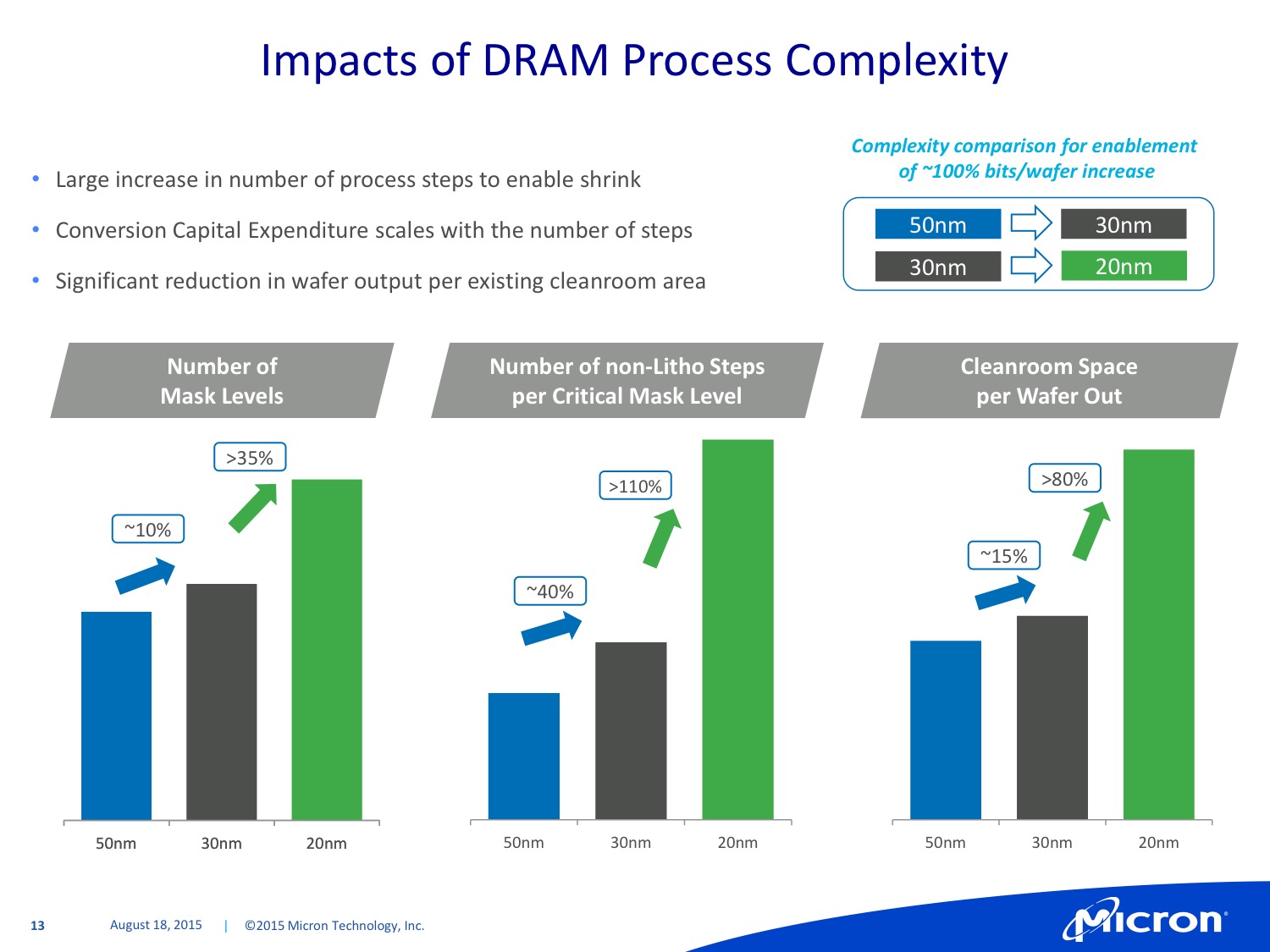

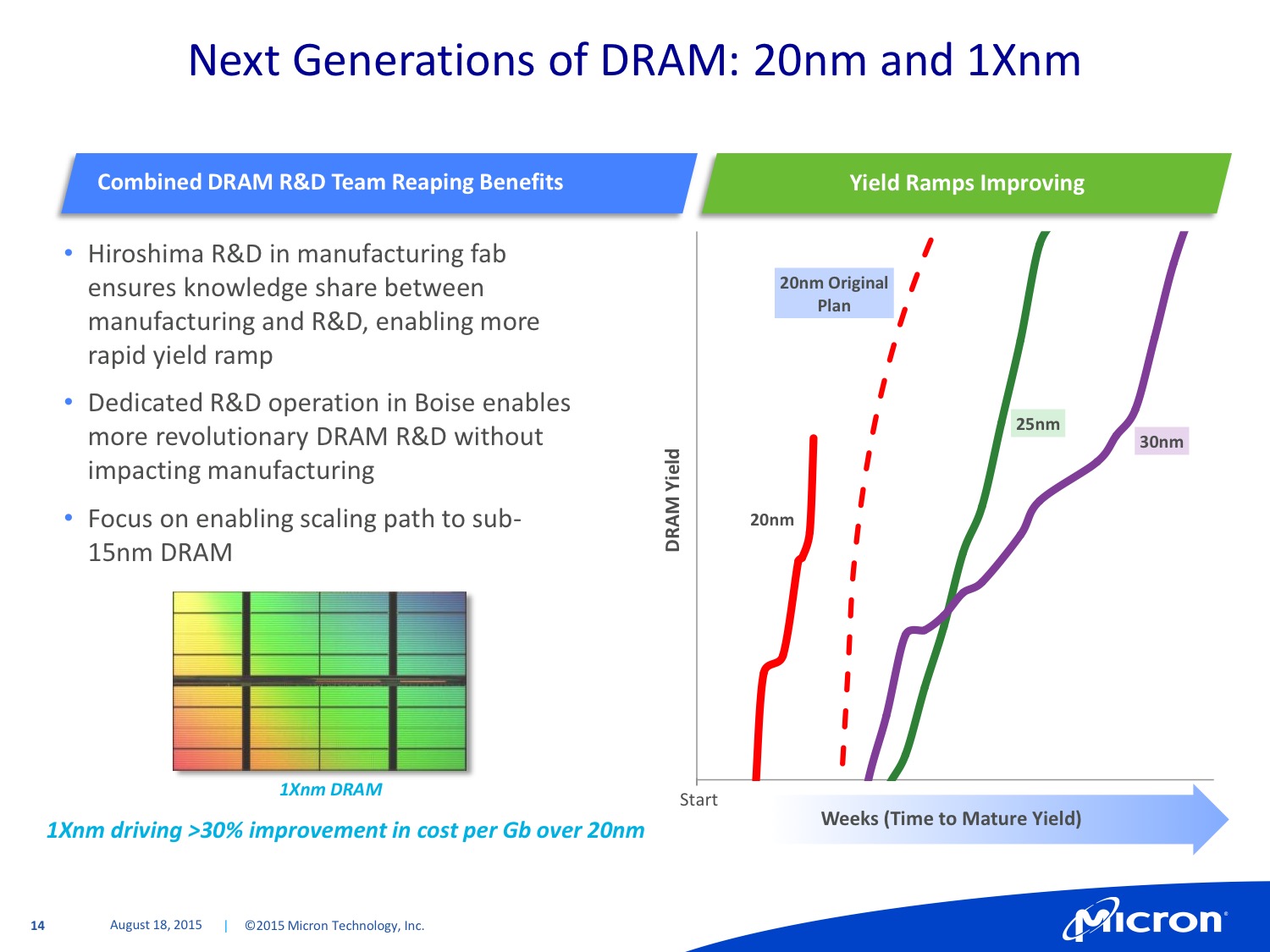

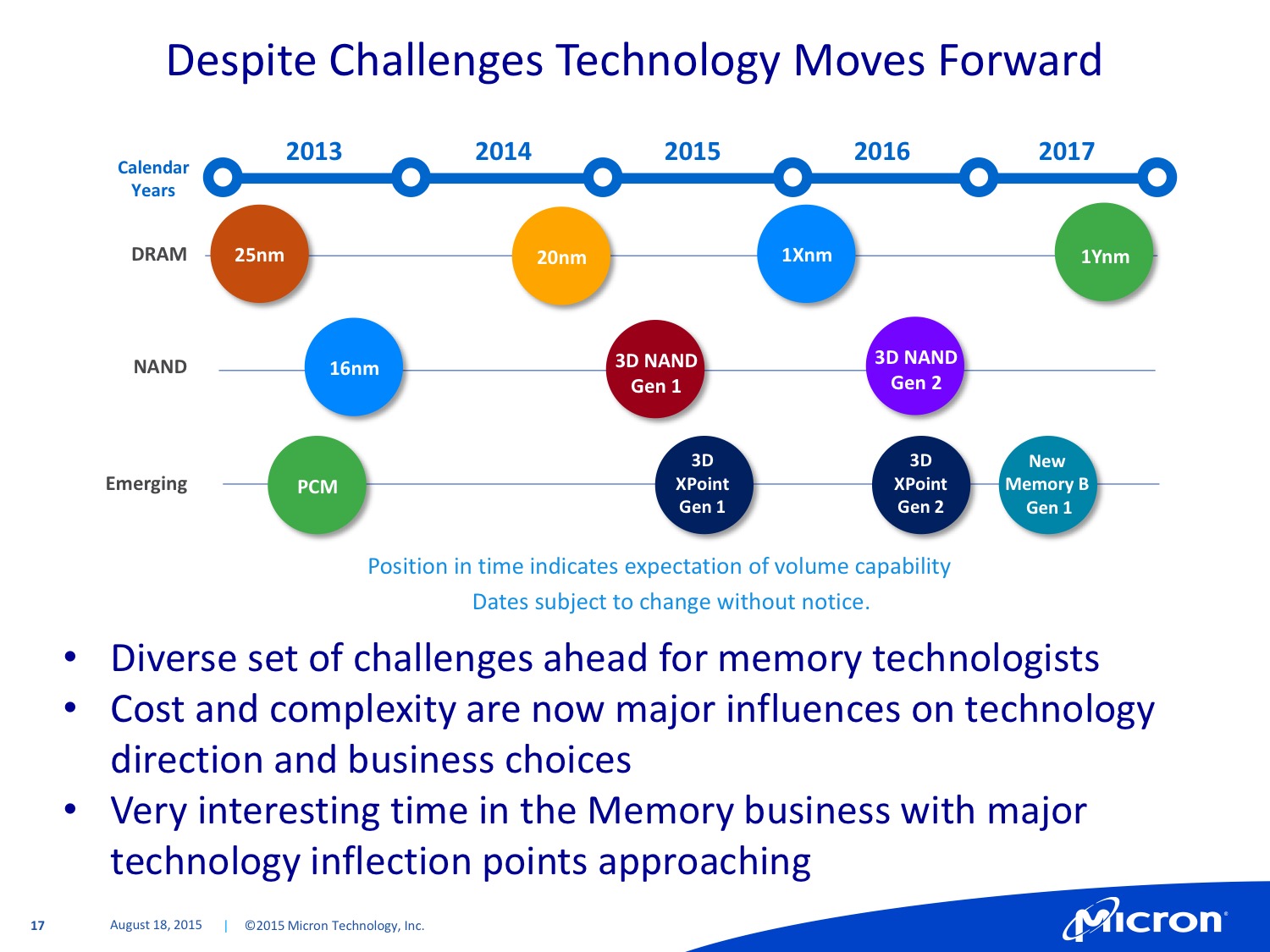

Micron est également revenu sur la complexité de la fabrication de la mémoire DRAM a 20nm et au dela. L'augmentation des coûts via les masques et les opérations rend de plus en plus difficile chaque passage à un nouveau node. Malgré tout le fabricant s'est felicité de ses yields atteint en 20nm et a indiqué travailler sur le 15nm et au delà.

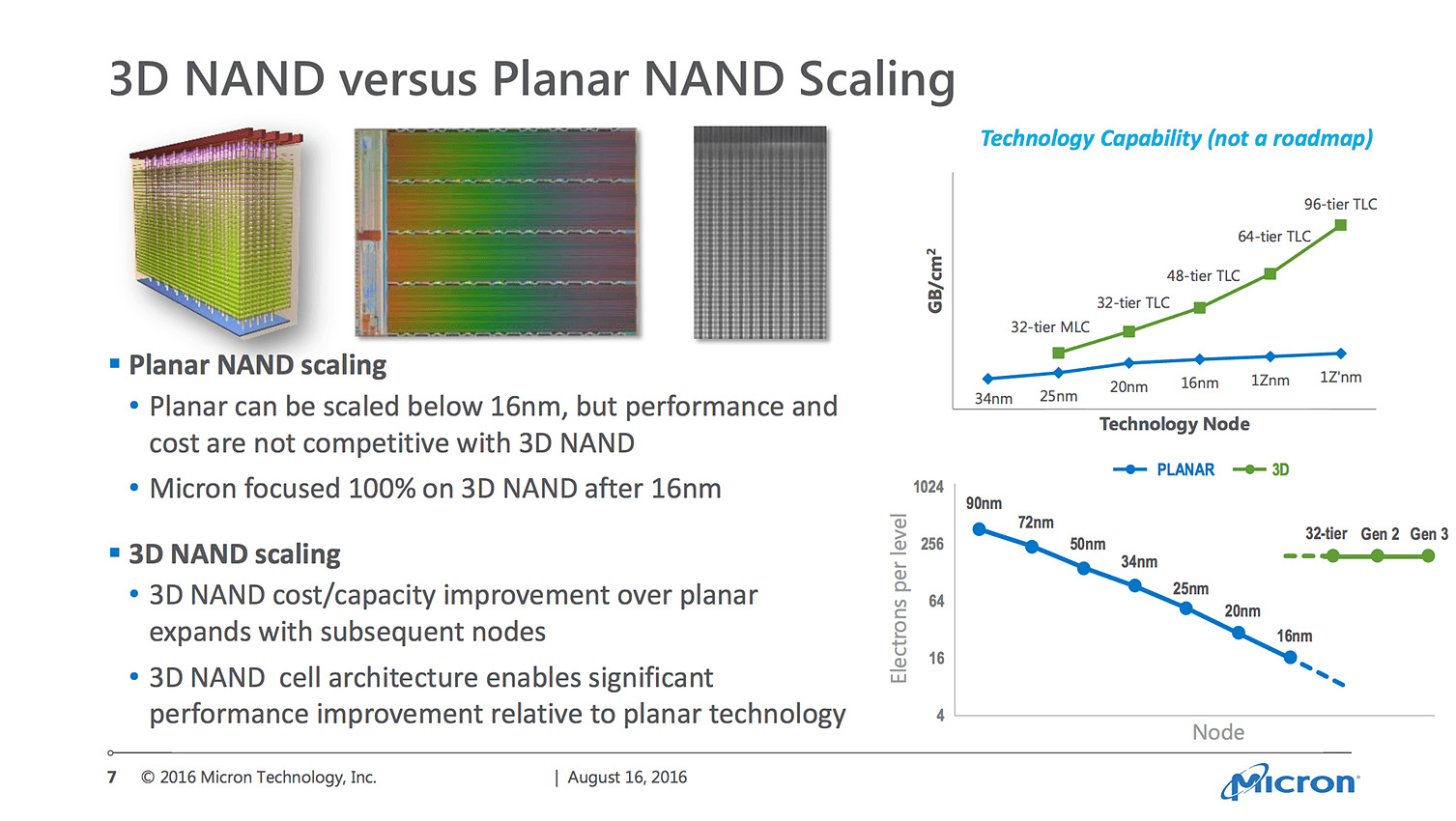

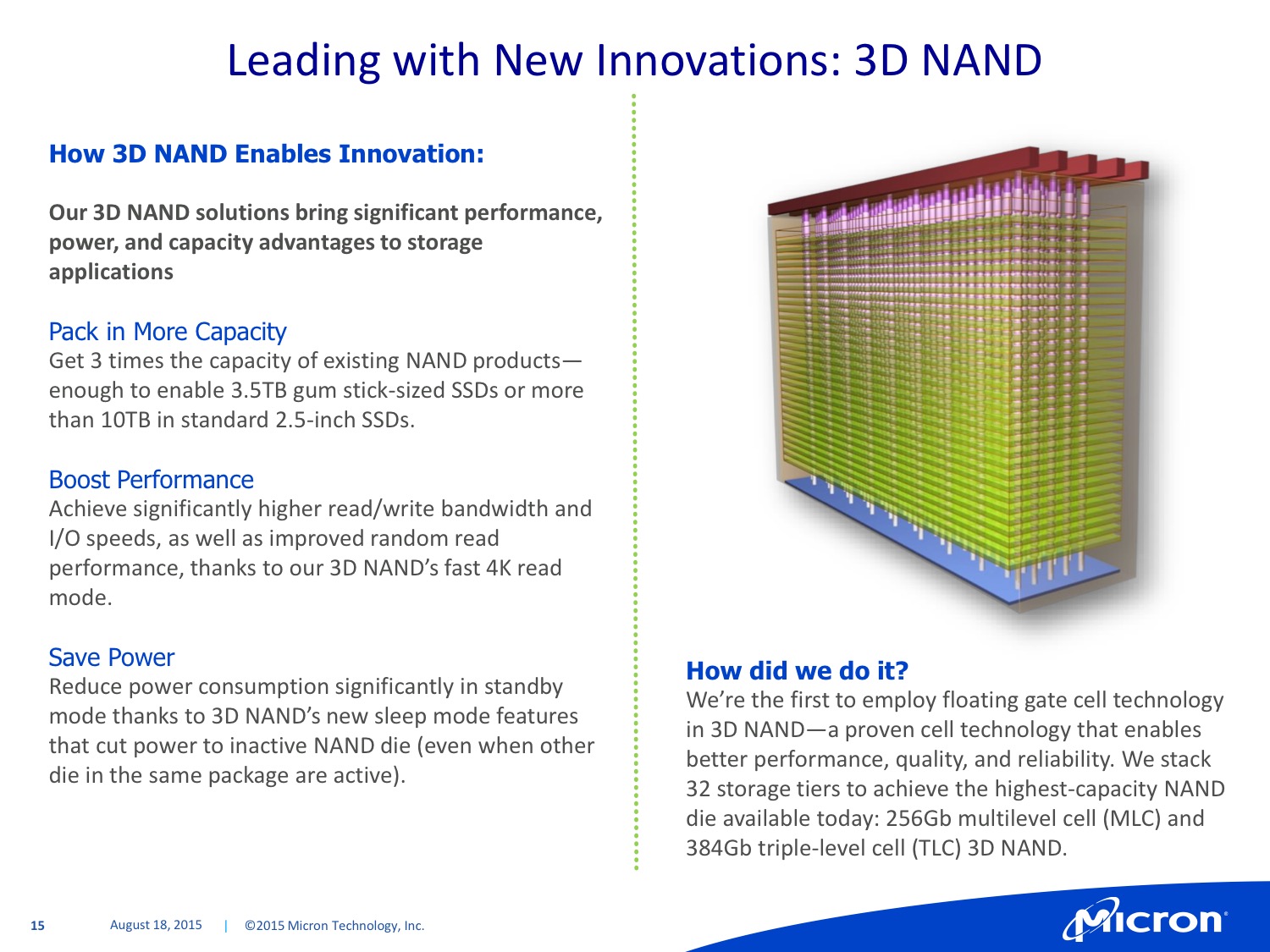

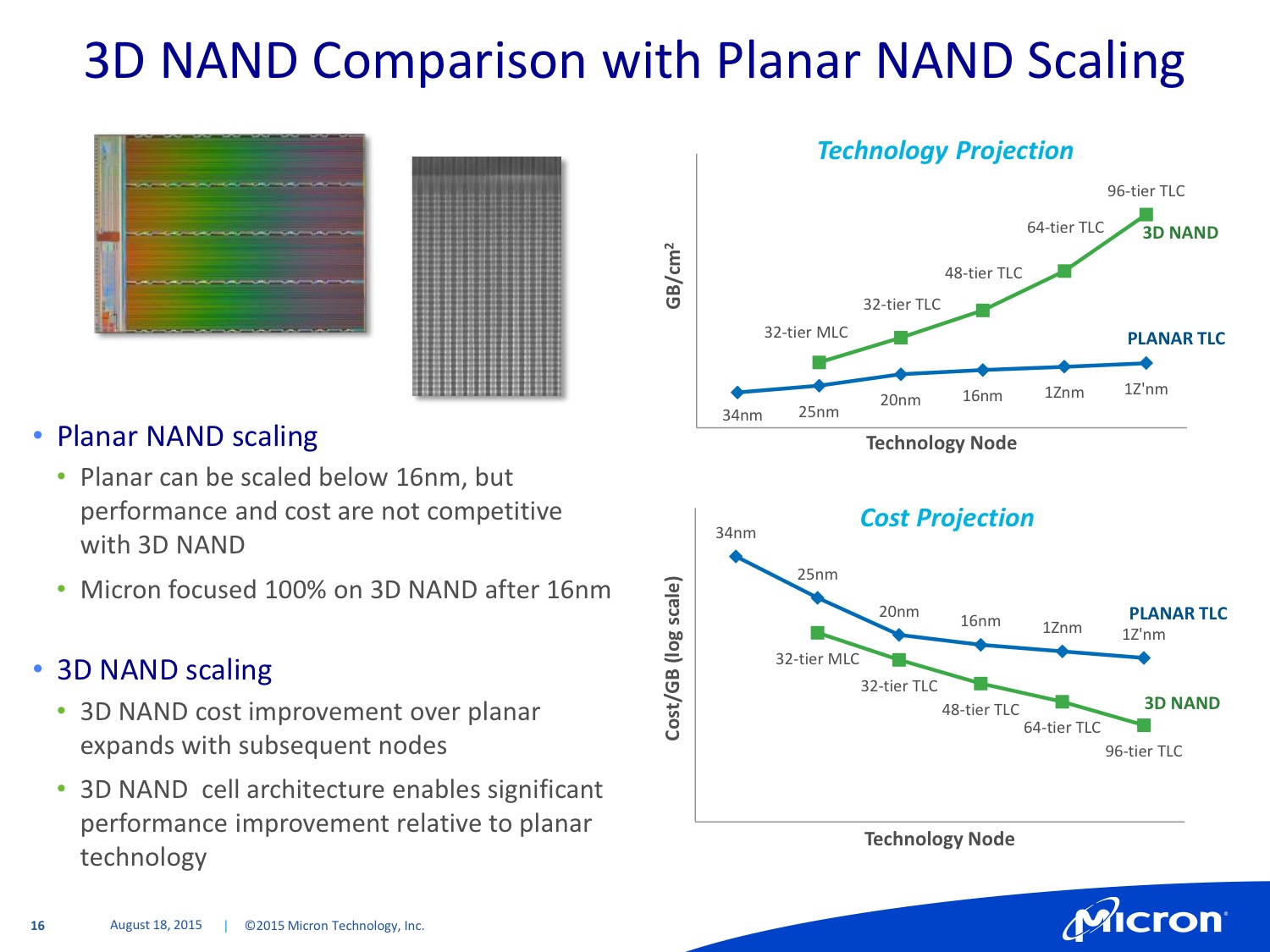

Côté NAND, Micron a confirmé que le 16nm serait son dernier node « traditionnel » et qu'il passait au delà à une gamme 100% 3D NAND. Cette variante de la NAND permet pour rappel de construire les cellules verticalement pour les empiler en augmentant la densité. Un avantage important qui permet d'utiliser des process plus anciens, et mieux maitrisés, autour de 50nm pour la première génération de Micron. La seconde génération de 3D NAND apparaitra en 2016.

3D XPoint a été peu évoqué, si ce n'est sur le fait qu'il y aura une seconde génération de cette mémoire en 2016. On notera que Micron parle toujours sur ses roadmaps d'une seconde nouvelle mémoire qui arriverait en 2017. Une variante de STTRAM (Spin Transfer Torque RAM) semble être l'une des possibilités, il faudra attendre un peu avant d'en savoir plus !