Les derniers contenus liés aux tags IMFT et TLC

16 Go en TLC 20nm chez Micron : 146mm²

Publié le 15/02/2013 à 10:02 par Marc Prieur

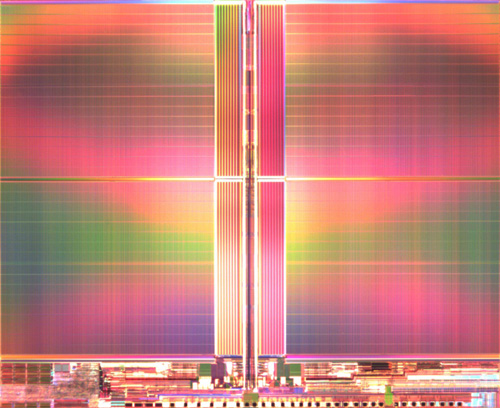

Micron avait déjà annoncé une puce de NAND de 16 Go gravée en 20nm, c'était en décembre 2011, et cette mémoire utilisait la technologie MLC (2 bits par cellule). Aujourd'hui le fondeur annonce une puce de 16 Go (128 Gb) qui utilise la TLC (3 bits par cellule). Elle ne mesure que 146mm², soit une baisse de la surface supérieure à 25% par rapport à la même puce en 20nm MLC.

A titre de comparaison une puce 8 Go en MLC et 25nm est à 167mm², la densité augmente donc par un facteur de 2,29 ce qui devrait permettre de faire sensiblement baisser le coût au Go. Actuellement en cours d'échantillonnage, cette puce sera produite en volume à compter du second trimestre.

Il faut noter qu'elle combine deux désavantages en terme de performances et de longévité : d'une part, du fait de la technologie TLC par rapport au MLC, Micron ne communiquant d'ailleurs pas sur son endurance, d'autre part parce que les puces de 16 Go utilisent des pages de 16 Ko, contre 8 et 4 Ko pour les puces de 8 et 4 Go. Pour rappel une page est la plus petite unité lisible et programmable d'une puce Flash.

Pour le moment il n'est pas question d'une utilisation dans les SSD, Micron la destinant au stockage amovible (cartes mémoires et clés USB), un marché qui devrait tout de même monopoliser 35% de la Flash en 2013.

MLC 3BPC en 25nm chez IMFT

Publié le 18/08/2010 à 13:47 par Marc Prieur

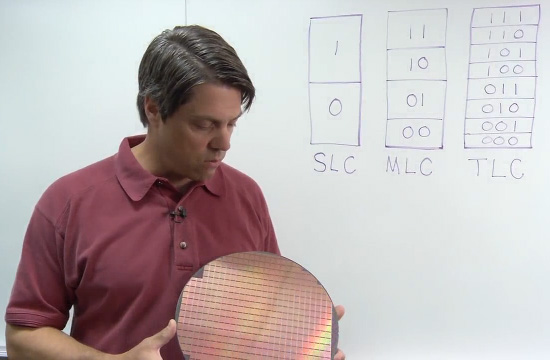

Après avoir annoncé une première puce Flash NAND MLC capable de stocker 3 bits par cellule (MLC 3BPC) en octobre 2009, la joint-venture Intel / Micron, IMFT (IM Flash Technologies), revient à la charge avec une nouvelle puce de ce type. La finesse de gravure passe de 34nm à 25nm, et la capacité de 4 à 8 Go.

Ce type de mémoire, également appelé TLC pour triple-level cell, permet de réduire notablement la taille du die pour une capacité identique, puisqu'elle ne mesure que 131mm², contre 167mm² pour une puce en 2 bits par cellule. A titre de comparaison, la puce TLC de 4 Go en 34nm mesurait 126mm².

Cette puce est actuellement en cours d'échantillonnage, alors que la MLC 25nm classique échantillonnée dès février est en production depuis mai. Elle devrait entrer en production d'ici à la fin de l'année. Il faut préciser que pour le moment, ce type de mémoire reste réservé aux clefs USB, aux lecteurs MP3 et aux cartes mémoires.

En effet, comme le passage de SLC (1 bit par cellule) à la MLC (2 bits par cellule), le passage de la MLC à la TLC (3 bits par cellule) abaisse les performances en écriture ainsi que l'endurance des cellules. Si aucun chiffre n'a été publié pour cette puce, Micron parlait début 2009 de performances divisées par 2 et d'endurance divisée par 10 ... voilà qui interdit donc leur utilisation au sein de SSD, à moins que la recette miracle d'Anobit fonctionne en pratique !