Les derniers contenus liés au tag IDF 2014

IDF: Détails sur les changements de Broadwell

IDF: USB 3.1, Power Delivery et Type-C

IDF: Skylake se montre à l'ouverture de l'IDF

IDF: Intel lance les Xeon E5-1600/2600 v3

UniDIMM, DDR3, DDR4 et LPDDR3 sont sur une barrette...

IDF: La DDR4 moins chère et devant la DDR3 en 2016 ?

IDF: Cohabitation Broadwell-K et Skylake

IDF: Stepping F du Core M

IDF: Le TDP compliqué du Core M

UniDIMM, DDR3, DDR4 et LPDDR3 sont sur une barrette...

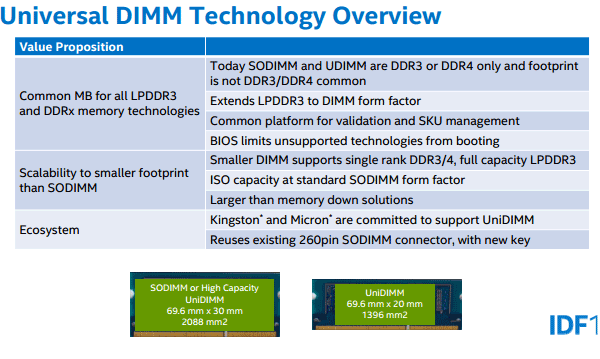

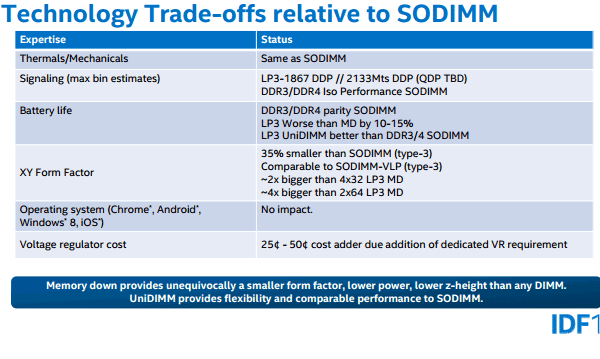

Lors de l'IDF 2014, Intel a présenté son projet Universal DIMM, ou UniDIMM en version courte. Ce nouveau format de barrette, qu'Intel semble avoir mis au point hors de l'organisation de standardisation JEDEC, serait supporté par Kingston et Micron.

Sur le papier le principe est relativement simple, il s'agit d'avoir un même format de barrette pouvant être utilisé avec des puces DDR3, DDR4 et même LPDDR3. Deux formats sont prévus :

- UniDIMM 69.6x20mm

- High Capacity UniDIMM 69.6x30mm

Les tailles reprennent en fait les formats SODIMM-VLP et SODIMM, et c'est d'ailleurs également le même nombre de contacts qui sont présent, 260. Le détrompeur n'est par contre pas situé au même endroit.

Avoir un format de barrette mémoire "universel" permettrait à Intel de faciliter la vie des OEM notamment puisque Skylake devrait supporter selon les versions la LPDDR3 (version Y, basse consommation pour portables), la DDR3/DDR4/LPDDR3 (version U, portables toujours mais classiques), la DDR4/LPDDR3 (version H, portable haute performance) ou encore la DDR3 et DDR4 (sur desktop).

La contrepartie serait selon Intel uniquement un surcoût au niveau de la régulation de tension de la carte mère de l'ordre de 0.25 à 0.5$. Le principe de l'UniDIMM est donc intéressant sur le papier, notamment sur portable ou il n'est pas vraiment possible d'intégrer divers types de connecteurs comme c'est le cas sur les cartes mères ATX on se souvient encore des cartes mères intégrant par exemple 4 DIMM DDR2 et 2 DIMM DDR3 ! Les PC de bureau ne sont a priori pas la cible première, mais on pourrait peut-être voir des cartes mères mini-ITX en UniDIMM.

Reste le problème de l'universalité qui n'est pas vraiment au rendez-vous contrairement à ce qu'indique la dénomination choisie par Intel, tout simplement parce que ce nouveau format n'a pas été standardisé par le JEDEC.

IDF: La DDR4 moins chère et devant la DDR3 en 2016 ?

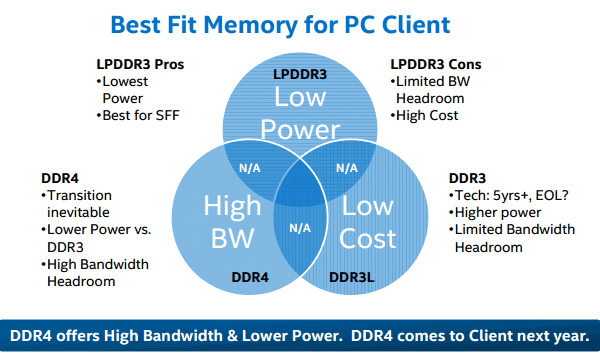

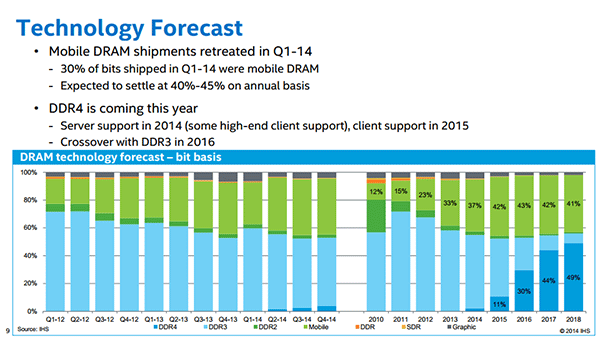

Lors d'une session consacrée à la mémoire DDR4, Intel a publiées quelques estimations provenant de l'institut IHS concernant la prise de pouvoir à venir de la DDR4 chiffres qu'il faut bien entendu prendre avec les pincettes d'usage.

Sur ce premier extrait, on peut voir que les estimations de part de marché pour la DDR4 font état de 11% en 2015, 30% en 2016, 44% en 2017 et 49% en 2018. IHS prévoit que c'est en 2016 que la DDR4 commencera à se vendre plus que la DDR3, sachant que Skylake qui devrait supporter les deux types de mémoire est prévu pour le second semestre 2015.

On notera au passage que la mémoire spécialisée pour le segment mobile (LP DDR2, LP DDR3, etc.) devrait se stabiliser à un peu plus de 40% du marché à compter de 2015, alors que dans le même temps IHS prévoit une baisse notable de la mémoire graphique (GDDR5) en 2015 par rapport à 2014.

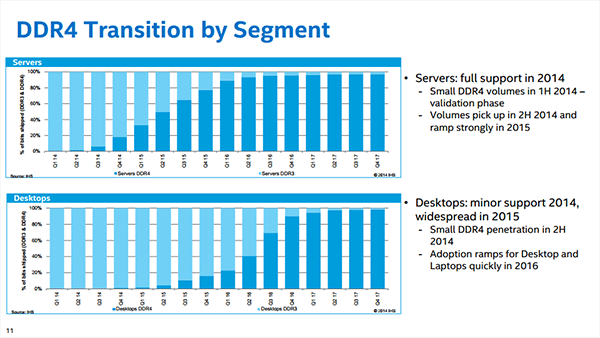

C'est logiquement sur les serveurs que la transition se fera en premier puisque les nouveaux Xeon LGA 2011-v3 ne gèrent que la DDR4, la DDR4 prenant le pas sur la DDR3 à partir de mi-2015. Sur PC de bureau ce n'est toutefois qu'à compter du troisième 2016 que la DDR4 dominera.

Côté densité cette fois, les puces de 1 Go pointent le bout de leur nez. On ne devrait a priori les trouver qu'en DDR4, elles permettront de mettre au point des barrettes classiques (Unbuffered) de 16 Go, avec un minimum situé à 8 Go. IHS prévoit qu'en 2016 elles représenteront 55% de la production contre 38% pour les puces de 512 Mo actuellement très majoritaires.

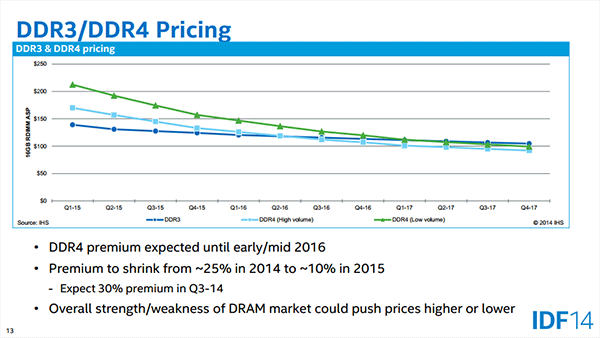

Côté tarif, IHS donne une estimation du surcoût d'une barrette 16 Go en RDIMM en DDR4 par rapport à la DDR3. Cette fois deux scénarios sont utilisés, l'un avec une adoption rapide de la DDR4 et l'autre avec une adoption lente de la DDR4. Dans le cas d'une adoption rapide, c'est à compter du second trimestre 2016 que la DDR4 et la DDR3 seraient au même tarif, avec un écart réduit dès le quatrième trimestre 2015, par contre il faudrait attendre le premier trimestre 2017 en cas d'adoption lente, avec un écart réduit à compter de troisième trimestre 2016. Ensuite c'est la DDR4 qui serait la moins onéreuse, sous l'action combinée de volumes plus importants et de puces profitant d'une densité accrue et des avancées de process là ou la DDR3 devrait stagner.

[ Carte trèès grise très grise ] [ test ]

IDF: Cohabitation Broadwell-K et Skylake

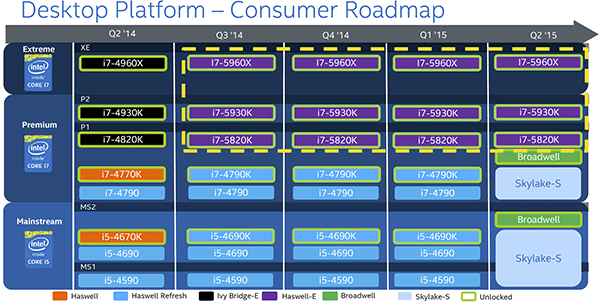

Une autre question brulante à laquelle nous espérions obtenir une réponse est la situation des plateformes desktop grand public d'Intel pour 2015. En effet si sur le haut de gamme les Haswell-E ont été lancés, le remplacement de Haswell en LGA1150 par ses versions 14nm est plus flou.

Pour rappel, Intel a fait le choix de ne décliner son architecture Broadwell côté desktop que sur des modèles Broadwell-K, les modèles haut de gamme dédiés à l'overclocking et qui auront la particularité d'intégrer le GPU Iris Pro (avec son cache L4). Broadwell ne sera pas décliné sur desktop au delà de ces modèles haut de gamme, qui seront probablement au nombre de deux comme à l'habitude. L'existence de ces modèles Broadwell-K est pour rappel un argument de vente pour les cartes mères Z97 d'Intel qui supporteront ces puces. Aux dernières nouvelles, le lancement de ces puces est prévu pour le troisième trimestre 2015 et Intel n'a pas apporté de précisions supplémentaires à son planning durant l'IDF.

Pour rappel, le tick en 14nm qu'est Broadwell sera suivi d'un tock en 14nm, Skylake qui lui aussi est prévu pour 2015. La conférence d'ouverture de l'IDF a été l'occasion pour Intel de confirmer que Skylake sera mis en production - et lancé - dans la seconde moitié de l'année 2015. Lors d'une table ronde avec Kirk Skaugen (Senior Vice President et General Manager du PC Client Group) il nous a été confirmé que les modèles desktop font partie des Skylake prévus pour 2015. Par contre, interrogé sur la cohabitation entre Broadwell-K et Skylake, et le lancement des Skylake-K, le responsable n'a pas voulu s'engager indiquant que ce genre de détails serait fourni un peu plus tard lorsque l'on approchera du lancement. Entre deux portes, on aura entendu que le plan actuel est de conserver Broadwell-K deux trimestres avant de le remplacer par Skylake-K. Le lancement des Skylake non K (Skylake-S) était censé intervenir avant, au second trimestre ce qui n'est plus le cas.

La roadmap de juin d'Intel et sa superposition de Broadwell-K et de Skylake-S

Il faut dire qu'Intel se retrouve dans une situation curieuse. On rappellera que Skylake n'utilisera pas le même socket que Haswell et Broadwell puisque le constructeur aurait supprimé les FIVR (régulation de tension intégrée) dans Skylake qui utilisera sur desktop le Socket LGA1151. On se retrouvera donc avec trois sockets qui cohabiteront potentiellement, en ordre de prix LGA1151, LGA1150 et LGA2011v3. Il sera intéressant de voir si Intel profitera du retard de Skylake sur son planning original pour proposer, par exemple en fin d'année 2015, un lancement simultané de Skylake-S et Skylake-K.

IDF: Stepping F du Core M

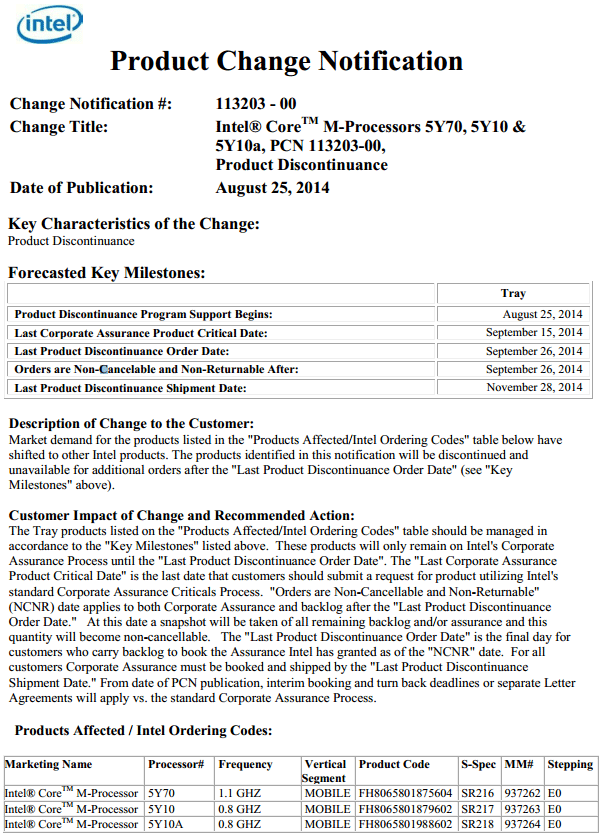

Au-delà du TDP, l'autre interrogation concernant le lancement des Core M par Intel était ce fort curieux PCN qui indiquait la fin de vie plus que prématurée, au 26 septembre, des processeurs qui venaient tout juste d'être annoncés.

Par deux fois, on nous a confirmé que ce PCN annonce en réalité un nouveau stepping de Broadwell-Y, le stepping F, lié à des changements sur le process 14nm. Il faudra attendre un peu plus pour savoir quels sont les changements précis, la spec update du Core M n'évoquant pas encore ce stepping F. Si les changements autour du process sont permanents, notamment pour améliorer les rendements de production, il est assez rare de voir de nos jours chez Intel un stepping justifié par le process.

La mention au sein du PCN d'une demande de marché ayant évolué vers d'autres modèles est selon Kirk Skaugen (Senior Vice President et General Manager du PC Client Group) probablement liée à un document réalisé à partir d'un modèle générique. Il est vrai qu'on retrouve habituellement ce genre de formulation dans les PCN annonçant la fin de vie de produit, mais en cas de simple transition de stepping le modèle est encore différent et fait référence aux nouveaux produits et aux changements apportés.

En l'état on ne sait donc pas si cette première fournée de Core M survivra au stepping F ou si elle sera remplacée par d'autres références, par exemple avec des fréquences différentes. La date d'arrivée du stepping F ne nous a pas été précisé, toutefois les rumeurs font état de début 2015, date à laquelle d'autres modèles de Core M sont attendus tout comme des Core de 5è génération basés sur Broadwell-U (un dual core plus classique avec notamment un TDP et des fréquences en hausse, un HD Graphics plus musclé et un chipset externe).

Tout ceci renforce l'impression que ce premier lot de Core M est là avant tout pour tenir la promesse du lancement de produits en 14nm avant la fin de l'année 2014, même si le process n'était pas encore techniquement au niveau espéré par le constructeur. Nous espérons qu'Intel clarifiera dans les semaines à venir les changements et éventuels nouveaux produits engendrés par ce stepping F.

IDF: Le TDP compliqué du Core M

Une des interrogations lors de l'annonce du Core M par Intel la semaine dernière concernait le TDP assez impressionnant annoncé pour ces premiers processeurs Broadwell, à savoir « seulement » 4.5 watts. Une valeur qui pouvait paraitre particulièrement basse pour un processeur qui n'est pas un Atom, particulièrement quand la génération précédente en Haswell ne passait pas sous les 11.5 watts de TDP

mais disposait d'un SDP de 4.5 watts.

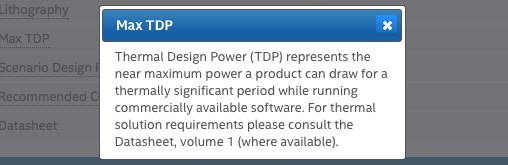

A la réponse de savoir quel est exactement le TDP du Core M, il conviendrait de savoir réellement ce que ce mot veut dire. En effet cette valeur a été fortement maltraité par de nombreux constructeurs - principalement pour des raisons marketing - et plus récemment certaines techniques ont été ajoutées dans les processeurs pour jouer sur des paramètres d'inertie thermiques. Ceci sans compter l'ajout du SDP par Intel avec Ivy Bridge que nous n'avions pas manqué de critiquer ici . Qu'est ce donc que le TDP ? Prenons la définition officielle chez Intel sur son site ARK (il s'agit de la définition du Max TDP, soyons précis !) :

On parle ici de la puissance « quasi » maximale qui peut être tirée (du système d'alimentation) pour un temps donné significatif, en faisant tourner des logiciels disponibles dans le commerce. On notera rapidement l'ambiguité du quasi maximal, mais nous attirons votre attention sur le fait que l'on parle ici de puissance tirée du système d'alimentation, cela aura son importance par la suite.

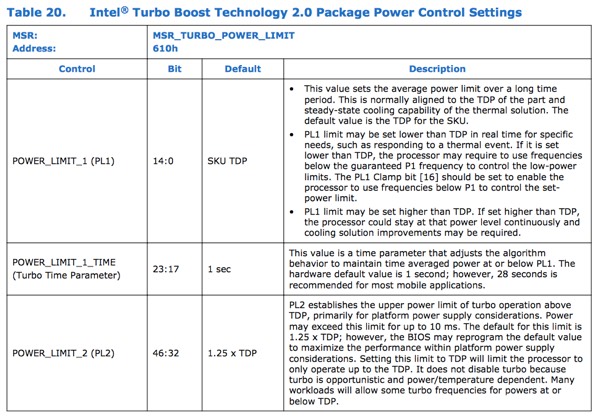

Pourquoi quasi ? La définition fait référence aux Datasheet (volume 1) d'Intel. Regardons celle des Core Y 11.5 Watts de génération Haswell :

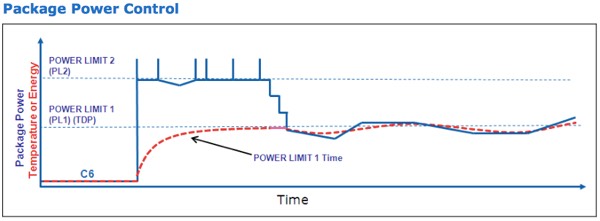

On retrouve deux Power Limit (PL1 et PL2). La première Power Limit correspond au « SKU TDP » (le TDP annoncé plus haut en Max TDP) et il s'agit de la valeur moyenne qui ne doit pas être dépassée sur une période donnée (par défaut, une tranche d'une seconde).

PL2 correspond à une surconsommation autorisée pour tirer partie de l'inertie thermique du processeur. Cette valeur est fixée à 1.25x le TDP (ce qui nous vaut la notion de quasi plus haut) et n'est autorisée que durant la montée en température du processeur. Il est possible de dépasser cette valeur pour des pics de 10 millisecondes. Tout ceci est résumé par ce diagramme :

La durée maximale d'un passage à PL2 (1.25x le TDP) est par défaut de 1.5x le PL1 Time (qui est par défaut sur Haswell-Y d'une seconde, soit 1.5 secondes au total, mais qui peut être augmentée, Intel recommandant 28 secondes pour les applications mobiles).

Comparons maintenant a la spec Core M :

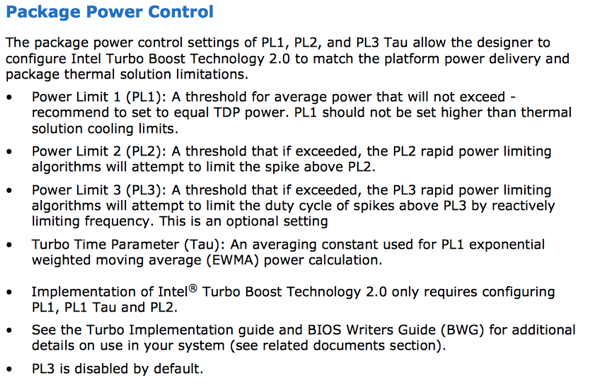

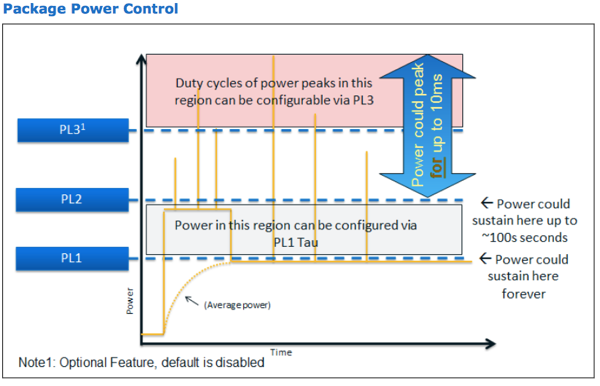

Plusieurs changements. On notera d'abord l'arrivée d'un PL3 optionnel qui sert a protéger la batterie et qui est désactivé par défaut. Ensuite, si la définition de la valeur PL1 est toujours recommandée comme étant égale au TDP, il n'y a plus de valeur par défaut indiquées pour PL2 (anciennement 1.25x le TDP) ou le PL1 Time (appelée PL1 Tau ici). Le schéma évolue également :

On notera ici que le PL2 est indiqué comme pouvant être soutenu en théorie pendant des centaines de secondes, dépendant de la valeur PL1 Tau sans plus de précisions. Là encore un indice potentiel sur la manière d'optimiser les performances, calculer une moyenne sur un temps plus large laisse de plus fortes opportunités pour obtenir des périodes de système idle pour « maintenir » la moyenne.

Reprenons maintenant le slide qui nous avait tant intrigué plus tôt :

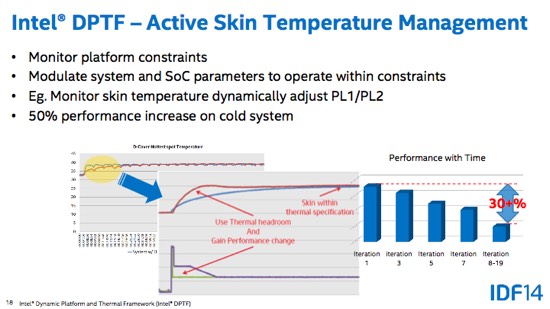

Intel utilise déjà sur les solutions précédentes un driver baptisé DPTF qui peut être utilisé pour reconfigurer le TDP d'une puce (un pilote open source que l'on peut trouver ici ). Jusqu'ici il servait notamment au cTDP (configurable TDP) et aussi à un mode Low Power (LPM).

La nouveauté de Broadwell concerne l'Active Skin Temperature Management qui étend le rôle du driver DPTF pour prendre en compte la température du système, en plus de la température du processeur qui était déjà prise en compte. Dans ce cas, DPTF peut faire varier les valeurs PL1 et PL2 pour « profiter » de l'inertie thermique du châssis (en plus de l'inertie thermique du processeur). En clair, la spécification permet de dépasser le TDP annoncé dans la durée en redéfinissant les valeurs PL1 et PL2 ! De combien, et dans quelles circonstances n'est pas une information que nous avons pu obtenir. On nous aura tout de même indiqué qu'en pic maximal, ces puces pouvaient avoir une consommation de 15 watts sur une durée de 10 millisecondes et que les plateformes devaient être prévues électriquement pour cette charge.

Ainsi, nous avons pu mettre nos mains sur des prototypes de telles plateformes dont l'arrière entier du châssis servait de dissipateur thermique au système, la sonde de « skin température » étant placée sur la carte mère. Si nous n'avons pas pu choisir les benchs qui tournaient sur ces plateformes ou utiliser des outils de monitoring pour évaluer la consommation en pratique, il semblait clair que ces tablettes pouvaient s'échauffer au delà de ce que l'on attendrait pour 4.5 watts en charge.

Bien entendu, l'idée de base d'Intel qui consiste a rajouter une seconde gestion de l'inertie thermique, celle du châssis, en sus de celle du processeur, pour maximiser les performances est loin d'être inintéréssante, pour ne pas dire qu'elle est astucieuse, mais l'on ne peut s'empêcher de noter que cela ne fait que rajouter une couche de flou supplémentaire sur la notion de TDP déjà fortement malmenée, tout en déportant ce gain de performances sur la qualité (ou non) du châssis utilisé. Ainsi, un châssis comme celui de démonstration utilisé par Intel maximise fortement les performances et rien ne dit que les chiffres de performances de benchmarks que l'on nous a montré se retrouveront sur des designs finaux de constructeurs. Si la volonté d'optimiser d'Intel est louable, en pratique nous préfèrerions que le constructeur soit un peu plus clair sur ses spécifications qui deviennent fort difficilement lisibles !