IDF: Détails sur les changements de Broadwell

Publié le 10/09/2014 à 19:17 par Guillaume Louel

Intel a donné quelques détails sur les changements apportés par ses premiers processeurs Broadwell à être disponibles sur le marché, à savoir les Core M.

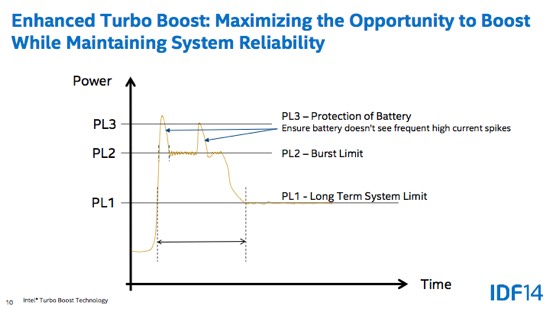

D'abord côté gestion de l'énergie, les Core M apportent quelques changements dans leur manière de réguler la fréquence. En plus des seuils de consommation « Burst » (pointe de consommation autorisée pendant quelques secondes) et de base (la consommation maximale autorisée en charge sur une charge prolongée), un troisième seuil PL3 a été défini présenté comme un seuil maximal autorisé afin d'éviter les pics de consommation pour la batterie.

Pour alimenter le processeur, on retrouve toujours sur les Core M des systèmes de régulation de tensions intégrés directement dans le processeur (FIVR) mais ceux ci évoluent. On passe en seconde génération avec quelques changements au niveau des heuristiques afin d'améliorer le rendement en régulant la tension d'alimentation unique (Vccin) . Le présentateur d'Intel expliquait d'ailleurs les challenges assez particuliers liés à l'utilisation d'un FIVR lorsque l'on consomme peu d'énergie, et qui ont poussé a l'ajout de régulateurs linéaires utilisés en mode C7+, un nouveau niveau d'économie d'énergie pour le package complet.

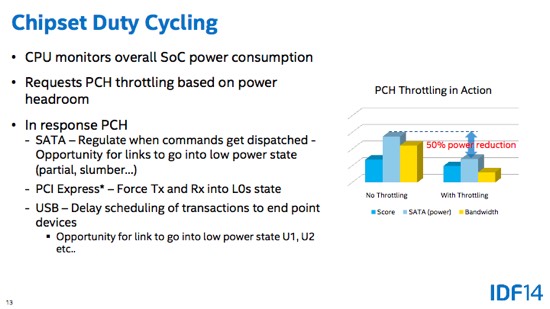

C'est là que l'on retrouve d'ailleurs le changement le plus surprenant : l'ajout d'un throttling au chipset ! La consommation est évaluée au niveau du package complet (pour rappel les Core M incluent le chipset dans le package) et des requêtes de throttling sont envoyées au chipset. ce dernier décide lui même son throttling en stoppant le PCI Express ou en groupant (avec un délai) les commandes SATA et USB pour les envoyer en une fois pour pouvoir couper les liens par la suite. On retrouve en général ce genre d'optimisations sur les plateformes mobiles type smartphone et tablette et il est bon de les voir également côté PC.

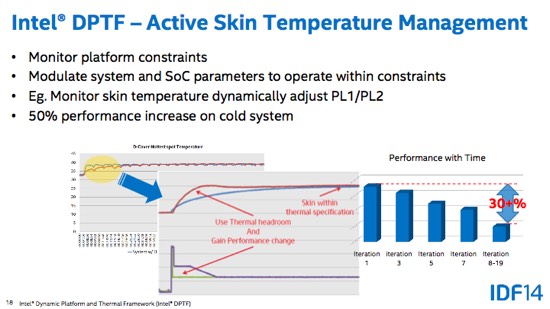

Notons enfin qu'Intel évoque avoir pris en compte la température totale du système en notant qu'un système « froid » peut être 50% plus performant qu'un système a température. Une variabilité des performances qu'on ne peut que regretter tant elle est massive et nous fait nous poser des questions sur la réalité du TDP annoncé par le constructeur.

Côté architecture, Intel a également donné quelques détails sur ce qu'apporte Broadwell face à Haswell en précisant les grandes lignes que l'on avait pu voir dans cette actualité.

On notera une réduction de la latence des multiplications en virgule flottante ainsi que des améliorations du côté des divisions côté latence et débit. Enfin, du côté des instructions dédiées à la cryptographie on retrouve quelques nouveautés avec notamment un nouveau générateur de nombres aléatoires.

Vos réactions

Contenus relatifs

- [+] 18/09: UniDIMM, DDR3, DDR4 et LPDDR3 sont ...

- [+] 13/09: IDF: La DDR4 moins chère et devant ...

- [+] 11/09: IDF: Cohabitation Broadwell-K et Sk...

- [+] 11/09: IDF: Stepping F du Core M

- [+] 11/09: IDF: Le TDP compliqué du Core M

- [+] 10/09: IDF: Détails sur les changements de...

- [+] 10/09: IDF: USB 3.1, Power Delivery et Typ...

- [+] 09/09: IDF: Skylake se montre à l'ouvertur...

- [+] 08/09: IDF: Intel lance les Xeon E5-1600/2...