IDF printemps 2009 à Pékin

Publié le 09/04/2009 par Damien Triolet

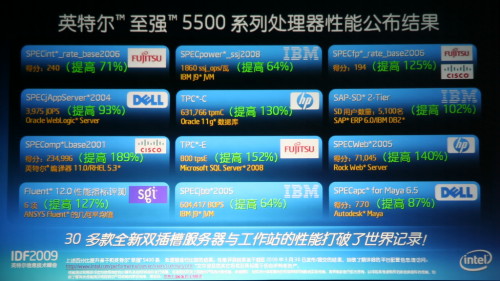

Nehalem-EXSi Pat Gelsinger est bien entendu revenu sur la famille Westmere fabriquée en 32 nanomètres, il na pas donné plus de détails à leur sujet par rapport à ce qui avait déjà été dévoilé par Intel. Il sest par contre étendu plus sur le côté serveur tout dabord en se félicitant des excellents résultats du Nehalem-EP, soit des Xeon 5500 qui devancent largement la concurrence et affichent des gains énormes par rapport à loffre précédente dIntel :

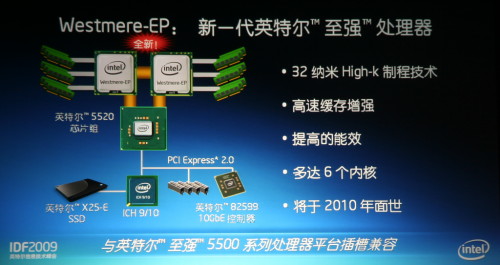

Pat Gelsinger a précisé que cette plateforme serait évolutive vers les Westmere-EP équipés de 6 cores au lieu de 4 puisquils reprendront un même socket.

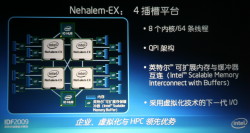

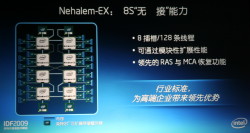

Plus haut dans la gamme, débarquera bientôt la plateforme à base de Nehalem-EX, soit la version 4 et 8 sockets de la famille qui a la particularité dêtre composée de 8 cores et donc de gérer 16 threads. Ces 8 cores sont associés à 4 liens QPI et 4 contrôleurs mémoire qui gèrent la technologie Intel Scalable Memory Interface. Un CPU très haut de gamme donc qui ne devrait souffrir daucune compétition.

La plateforme que nous avons pu voir en action était la version 4 sockets, ce qui représente donc au total 32 cores et 64 threads, de quoi bien encombrer le gestionnaire des tâches :

LarrabeePat Gelsinger a terminé son keynote par Larrabee en revenant tout dabord sur le jeu dinstruction vectoriel dédié qui a été dévoilé le mois passé. Celui-ci devrait selon lui combler tous les développeurs et permettre de tirer le meilleur de Larrabee avec sa centaine de nouvelles instructions spécifiques aux unités vectorielles 512 bits qui se trouveront dans chacun des cores de Larrabee.

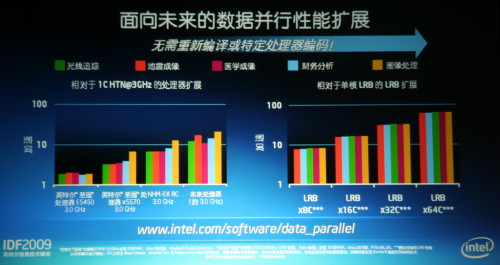

En plus de ce langage de bas niveau, Intel continue de développer Ct son langage de haut niveau destiné à exploiter les processeurs multicores et massivement parallèle. Intel est confiant dans le fait que ce langage deviendra un standard accepté par la communauté de développeurs et montrait des chiffres très bons au niveau de la scalabilité soit la faculté de profiter des cores supplémentaires. Ceci tant au niveau des CPUs multicores (Xeon dualcore vs X5570 quadcore vs Nehalem-EX octocores vs la future génération) que de Larrabee avec une progression des performances proportionnelle au nombre de cores (de 8 à 64).

Durant son keynote, Pat Gelsinger a brièvement sorti un wafer de Larrabee, précisant que celui-ci était bel et bien fonctionnel dans les labos dIntel. Quelques secondes après ce wafer avait disparu et a dailleurs été masqué dans le webcast publié sur le site dIntel. Nous avons pu en prendre une photo, mais malheureusement de loin. Cest dans cette situation quon regrette de ne pas être un officiel chinois assis au premier rang !

Nous pouvons néanmoins constater sur la photo que le die est énorme, nous pouvons lestimer à approximativement 600 mm² sur base de ce wafer de 300mm de diamètre soit un ordre de grandeur semblable à celui du GT200 de Nvidia fabriqué en 65 nanomètres et six fois supérieur à celui dun Penryn dualcore.

Reste la question du procédé de fabrication. Un die aussi imposant nous laisse penser quIntel nutilisera pas son nouveau procédé de fabrication 32 nanomètres mais plutôt le 45 nanomètres, dautant plus que Pat Gelsinger a précisé quIntel lancera sa première carte graphique à base de Larrabee à la fin de cette année ou au début de 2010. Dun autre côté le 32 nanomètres pourrait être nécessaire à Intel pour frapper fort. 48 cores en 45 ? 64 cores en 32 nanomètres ? Les paris pour la première génération Larrabee sont ouverts.

Sommaire

A lire également

Vos réactions

Contenus relatifs

- [+] 09/12: Guide : Les PC HardWare.fr !

- [+] 14/11: Qualcomm dit non à Broadcom

- [+] 13/11: Thermaltake lance une chaise venti...

- [+] 11/09: Microsoft confirme des problèmes de...

- [+] 30/08: PCI Express 5.0 pour 2019, débit do...

- [+] 01/08: Les taux de retour des composants (...

- [+] 11/07: Le minage consommerait plus que Par...

- [+] 04/07: ASUS XG-C100C, le 10GBASE-T à 120

- [+] 26/06: Computex et le PC : changement et c...

- [+] 24/03: Corsair lance ses PC One avec deux ...