AMD Athlon 64 FX-57

Publié le 27/06/2005 par Marc Prieur

Nouveau processeur, nouveau coreLes Athlon 64 Socket 754/939 ont déjà connus plusieurs changements de core au cours de ces dernières années. Le SledgeHammer et ClawHammer (1 Mo de cache L2) et le Newcastle (512 Ko de cache L2) étaient gravés en 130nm. Larrivée du 90nm sest faite petit à petit, via le core Winchester. Doté de 512 Ko de cache L2, il ne dépasse pas les 2.2 GHz sur un produit commercial, lAthlon 64 3500+ Socket 939.

Depuis quelques mois maintenant, on voit arriver des Athlon 64 basés sur un nouveau core. De révision « E », celui-ci est décliné sur Athlon 64 en une version avec 512 Ko de cache L2, le Venice, et une version avec 1024 Ko de cache L2, le San Diego. Contrairement au Winchester, les Venice et San Diego ne sont pas limités aux processeurs les plus bas de gamme mais sont désormais utilisés sur toute la gamme. Le San Diego ne se limite donc pas au nouvel FX-57, mais est également utilisé pour les autres A64 1 Mo, soit les FX-55, 4000+ et 3000+.

Diverses améliorations sont apportées par ce nouveau core, la première se situant au niveau de la fabrication et de lutilisation du Dual Stress Liner. Cette technique, mise au point par AMD et IBM est de type « strained silicon » et permet daugmenter la vitesse de déplacement des électrons dans le transistor et donc de faciliter la montée en fréquence et/ou de réduire la consommation.

Le contrôleur mémoire a également été amélioré. Auparavant, dans le meilleur des cas, 4 barrettes simple face (8 puces) étaient gérées en DDR400 2T, et 4 barrettes double faces (16 puces) en DDR333 2T. Dorénavant, il est possible dêtre respectivement en mode DDR400 1T et DDR400 2T avec ce type de barrettes. Pour rappel, 2T ou 1T signifie une latence de 2 cycles dhorloge ou de 1 cycle dhorloge pour le Command Rate, qui est la latence séparant la sélection de la RAM de lenvoi dune commande à celle-ci. Il ne sagit pas de la seule amélioration puisque AMD a également amélioré le pré chargement des données, ainsi que le nombre de write combining buffers.

Le dernier ajout est celui des instructions SSE3 dIntel. Les instructions SSE3 ne sont pas un nouveau jeu dinstructions à part entière mais plutôt un complément aux jeux dinstructions existants :

- 1 instruction x87 (FPU) pour la conversion de flottants en entiers (fisttp)

- 3 instructions SIMD 128 bits pour la duplication de données (movsldup, movshdup, movddup)

- 1 instruction SIMD 128 bits pour le chargement de données non alignées (lddqu)

- 2 instructions SIMD 128 bits pour laddition en calcul vertical (addsubps, addsubpd)

- 4 instructions SIMD 128 bits pour laddition / soustraction en calcul horizontal (haddps, hsubps, haddpd, hsubpd)

On notera que deux autres instructions SSE3 destinées à la synchronisation des threads, monitor et mwait, nont pas été intégrées par AMD au sein de ses Athlon 64 ainsi que de ses Athlon 64 X2 basés sur le core « E ».

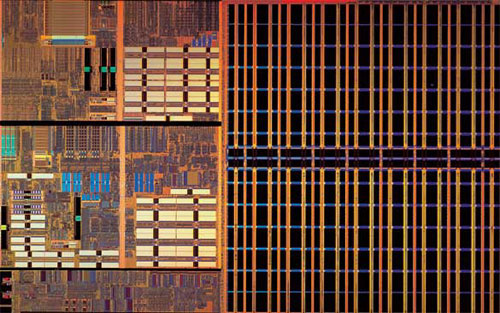

Au final, tout ceci entraîne un nombre de transistors plus conséquent : avec 1 Mo de cache, on passe de 105 à 114 millions de transistors, et avec 512 Ko de cache, de 68.5 à 76 millions. Du fait de la réduction de la finesse de gravure, les dies sont toutefois moins gros : on passe respectivement de 193 à 115mm² et de 144 à 84mm². Ceci entraîne bien entendu une baisse des coûts de production à taux de rendement équivalent puisquil est possible de graver plus de processeurs sur une même galette de silicium.

Sommaire

1 - Introduction

2 - Nouveau processeur, nouveau core

3 - Le FX-57, 130nm vs 90nm, Overclocking

4 - 3d studio max 7, Maya 6

2 - Nouveau processeur, nouveau core

3 - Le FX-57, 130nm vs 90nm, Overclocking

4 - 3d studio max 7, Maya 6

Vos réactions

Contenus relatifs

- [+] 09/05: AMD Ryzen 7 2700, Ryzen 5 2600 et I...

- [+] 04/05: Un Coffee Lake 8 coeurs en préparat...

- [+] 27/04: Le 10nm d'Intel (encore) retardé, l...

- [+] 26/04: Jim Keller rejoint... Intel !

- [+] 23/04: MAJ de notre test des Ryzen 7 2700X...

- [+] 20/04: MAJ de notre comparatif CPU géant

- [+] 19/04: AMD Ryzen 2700X et 2600X : Les même...

- [+] 19/04: 2008-2018 : tests de 62 processeurs...

- [+] 13/04: Les AMD Ryzen Pinnacle Ridge en pré...

- [+] 10/04: LGA4189 pour les Xeon Ice Lake !