Les derniers contenus liés aux tags 3D NAND et 3D XPoint

Des détails sur le 7nm à l'ISSCC 2017

Roadmap SSD Intel : 3D NAND et 3D Xpoint

La 3D NAND arrive chez Micron, MX300 en vue ?

IDF: Roadmap mémoire Micron

Des détails sur le 7nm à l'ISSCC 2017

La conférence ISSCC (International Solid-State Circuits Conference) se tiendra pour son édition 2017 du 5 au 9 février à San Francisco, et nos confrères d'EEtimes ont eu accès à l'avant programme.

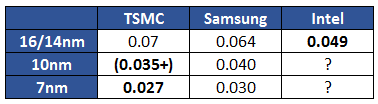

Comme tous les ans les acteurs du milieu des semi conducteurs y présenterons leurs nouveautés, et l'on notera que TSMC et Samsung présenterons leurs cellules SRAM (utilisées notamment pour la mémoire cache dans les puces). L'année dernière, Samsung avait proposé deux versions distinctes pour son process 10nm, optimisées pour la densité ou les performances, de 0.040 µm² et 0.049 µm².

D'après nos confrères, TSMC présentera une cellule SRAM 7nm de seulement 0.027µm², tandis que Samsung présentera une cellule SRAM 7nm de 0.030µm², mais fabriquée en EUV. D'après Samsung, l'EUV permettrait de diminuer la tension minimale nécessaire de 39.9mV (TSMC indique aussi des optimisations basse tension, on attendra la conférence pour comparer l'impact ou non de l'EUV).

La SRAM est un composant fondamental des puces et sa taille permet en général de se donner une bonne idée des process. Cependant il faut être assez méfiant, les constructeurs annonçant parfois des "records" de densité qu'ils n'utilisent pas forcément en production. Nous avons rapporté dans le tableau ci dessous les chiffres les plus bas (correspondant aux bibliothèques "hautes densité") pour TSMC, Samsung et Intel :

Par rapport au tableau, on notera qu'Intel n'utilise pas cette SRAM haute densité dans ses processeurs, mais de la SRAM 0.059 µm². Même en prenant cela en compte, Intel garde la meilleure densité à 16/14nm pour la SRAM. Le constructeur ne fournit pas encore d'infos sur ses futurs process.

TSMC n'a pas donné non plus de chiffre exact pour son 10nm, estimant simplement 50% de réduction par rapport à son 16nm sur la SRAM, ce qui nous vaut un chiffre entre parenthèses. Selon toutes vraisemblances, et conformément aux autres annonces sur la densité (2.1x d'après le constructeur), on estimera que TSMC devrait avoir une SRAM d'une taille légèrement inférieure à celle de Samsung.

Intel ne devrait pas effectuer d'annonce sur ce sujet lors de l'ISSCC, ce qui est assez dommage. Le constructeur devrait présenter les FPGA Altera Stratix 10 (14nm) tandis qu'AMD proposera une présentation plus en détails de Zen.

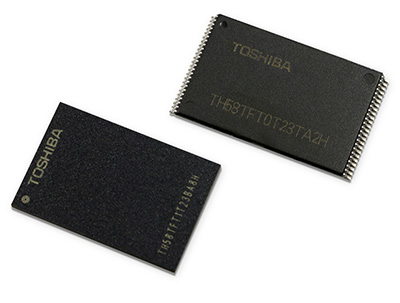

On notera aussi que Western Digital/Toshiba, ainsi que Samsung, présenterons des puces 3D NAND 512 Gbit TLC 64 couches. Dans le cas de Samsung, cette puce avait été annoncée cet été, plus de détails techniques devraient être disponibles. Pour Western Digital/Toshiba, cette puce avait été évoquée cet été comme objectif.

On notera que nos confrères pointent à raison un grand absent : une fois de plus, ni Intel, ni Micron, n'effectueront de présentation technique de leur mémoire 3D Xpoint !

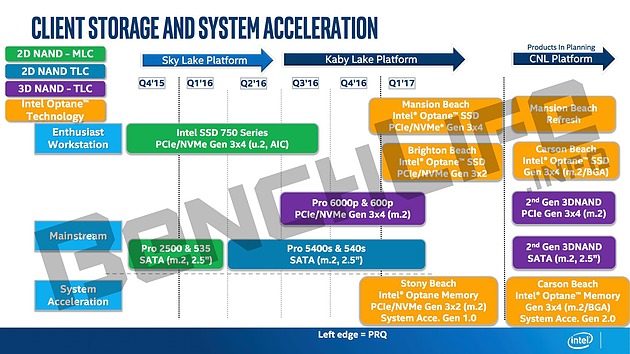

Roadmap SSD Intel : 3D NAND et 3D Xpoint

Benchlife a publié un extrait de roadmap Intel concernant les SSD. La prochaine sortie est prévue pour le troisième trimestre 2016, il s'agira des Pro 6000p et 600p qui seront des SSD au format M.2, interfacés en PCIe Gen3 x4 et utilisant un protocole NVMe. Ils utiliseront de la 3D NAND TLC.

Intel prévoit ensuite de décliner la technologie Optane, ayant pour base la mémoire 3D Xpoint, sur de nombreux SSD. Pas moins de 3 gammes seront lancées entre le dernier trimestre 2016 et le premier trimestre 2017. Tous utiliseront une interface PCIe Gen3 et un protocole NVMe, à commencer par Stony Beach au format m.2 (en PCIe x2) qui sera un accélérateur système : il s'agira donc d'un SSD de petite capacité faisant office de cache. Mansion Beach sera en PCIe x4 et il s'agira du haut de gamme, a priori sous forme de carte fille tout comme Brighton Beach qui lui se limitera au PCIe x2.

A plus long terme Intel prévoit ensuite de remettre à jour ces gammes pour la plate-forme Cannonlake fin 2017. Les Optane précédemment en PCIe x2 passeront au x4 et seront déclinés à la fois en m.2 et au format BGA, alors que côté NAND seule la 3D NAND TLC subsistera. Elle sera utilisée à la fois sur des SSD M.2 PCIe Gen3 x4 et des SSD M.2 et 2.5" SATA.

La 3D NAND arrive chez Micron, MX300 en vue ?

Nous l'indiquions il y a peu, la 3D NAND IMFT (Micron / Intel) semble prête puisque Intel a dégainé le premier avec une gamme de SSD professionnels l'utilisant. Micron affute également ses armes puisqu'il a indiqué hier lors d'un webcast qu'un nouveau SSD 2.5" grand public utilisant la 3D NAND arriverait en avril, probablement sous la dénomination Crucial MX300. La 3D NAND sera également déclinée en juin sur une gamme de SSD OEM en 2.5", M.2 et mSATA.

Par ailleurs Micron a annoncé ses premiers SSD PCIe NVMe, les Micron 9100 et 7100 qui sont destinés aux professionnels. Tous deux sont basés sur de la NAND MLC 16nm et sont destinés au monde professionnel. Le 9100 sera disponible en versions carte fille et 2.5", pour le 7100 ce sera 2.5" et m.2. Pour le 7100 Micron a précisé que le contrôleur utilisé serait un Marvell 88SS1093 et que les capacités iraient de 400 Go à 1,92 To en 2.5", 400 à 960 Go en m.2. La 3D NAND devrait pour sa part être intégrée dans des solutions professionnelles à compter du second semestre.

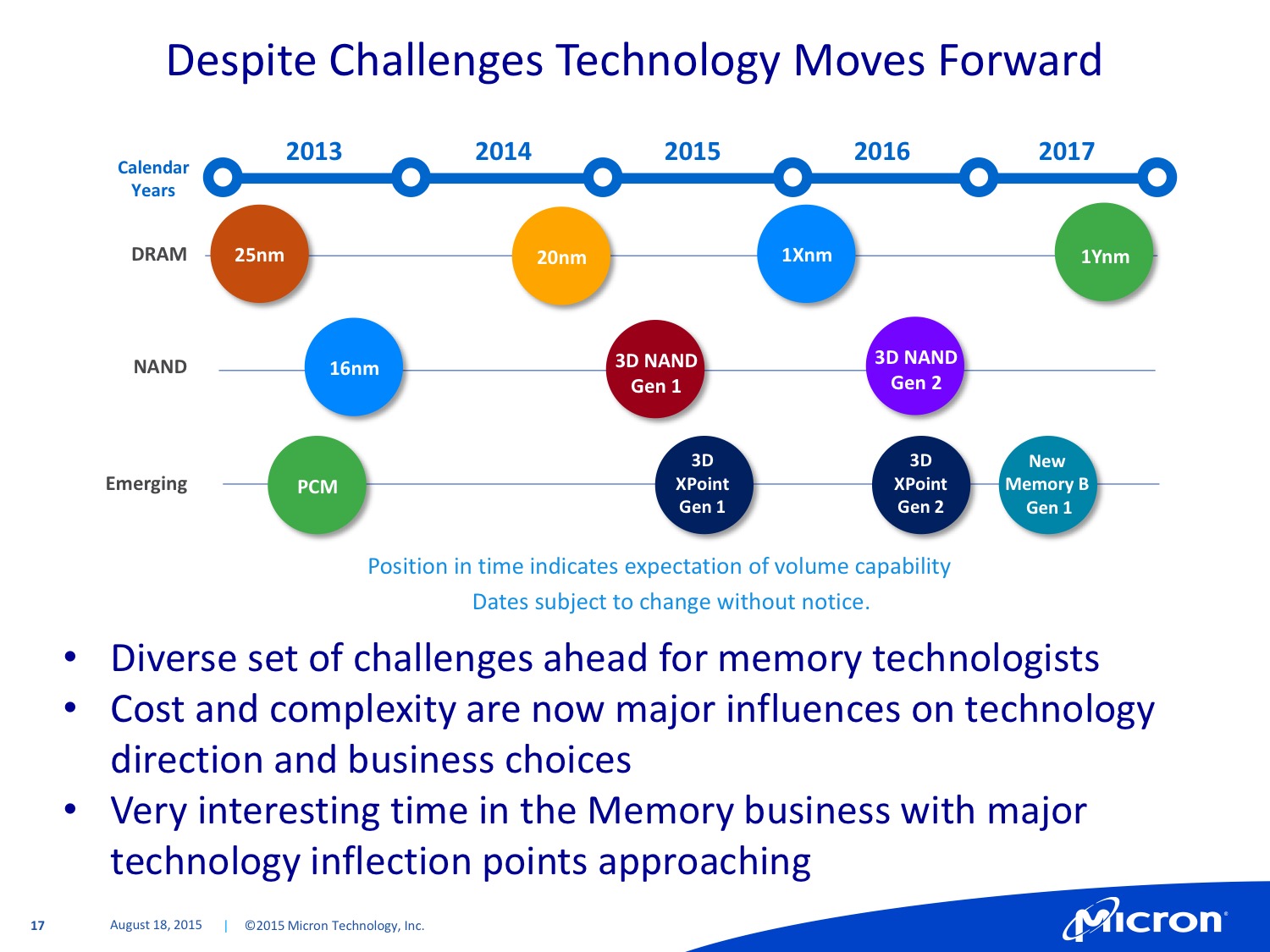

Concernant la PRAM 3D Xpoint annoncée en juillet 2015, Micron a précisé qu'on devrait la "voir" cette année, ce qui n'est pas forcément très clair. Rappelons que lors de l'annonce Intel et Micron avaient indiqués qu'elle était en production, avant que Micron ne précise en janvier dernier qu'il faudrait encore 12 à 18 mois pour lancer la production en volume.

IDF: Roadmap mémoire Micron

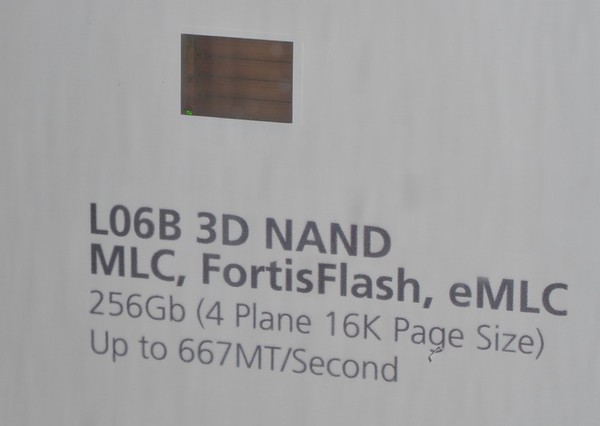

Le partenaire d'Intel sur la mémoire 3D XPoint était présent sur l'IDF avec un stand ou l'on pouvait apercevoir un wafer de NAND 16nm, ainsi qu'un module 3D NAND de 256 Gbits.

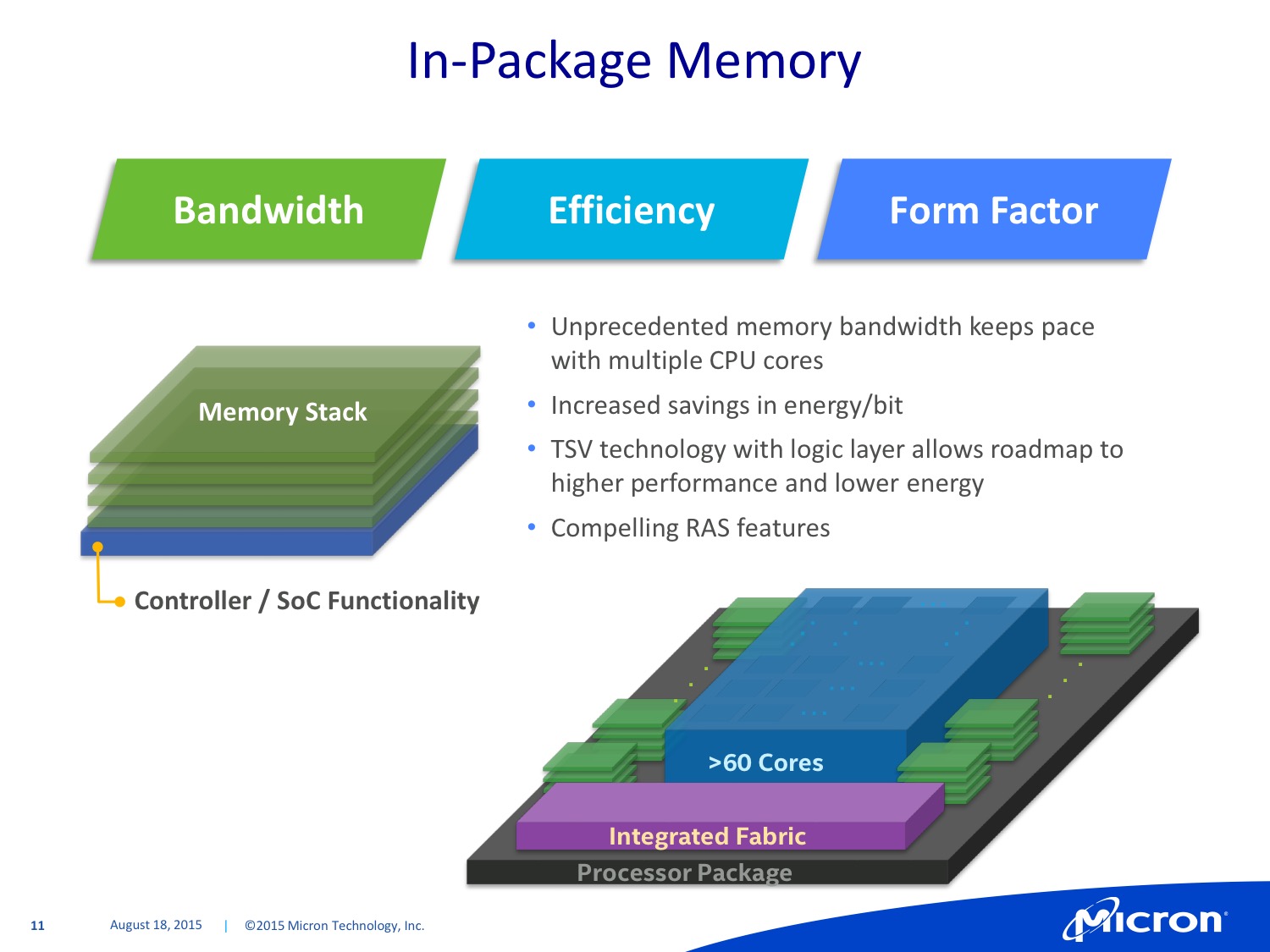

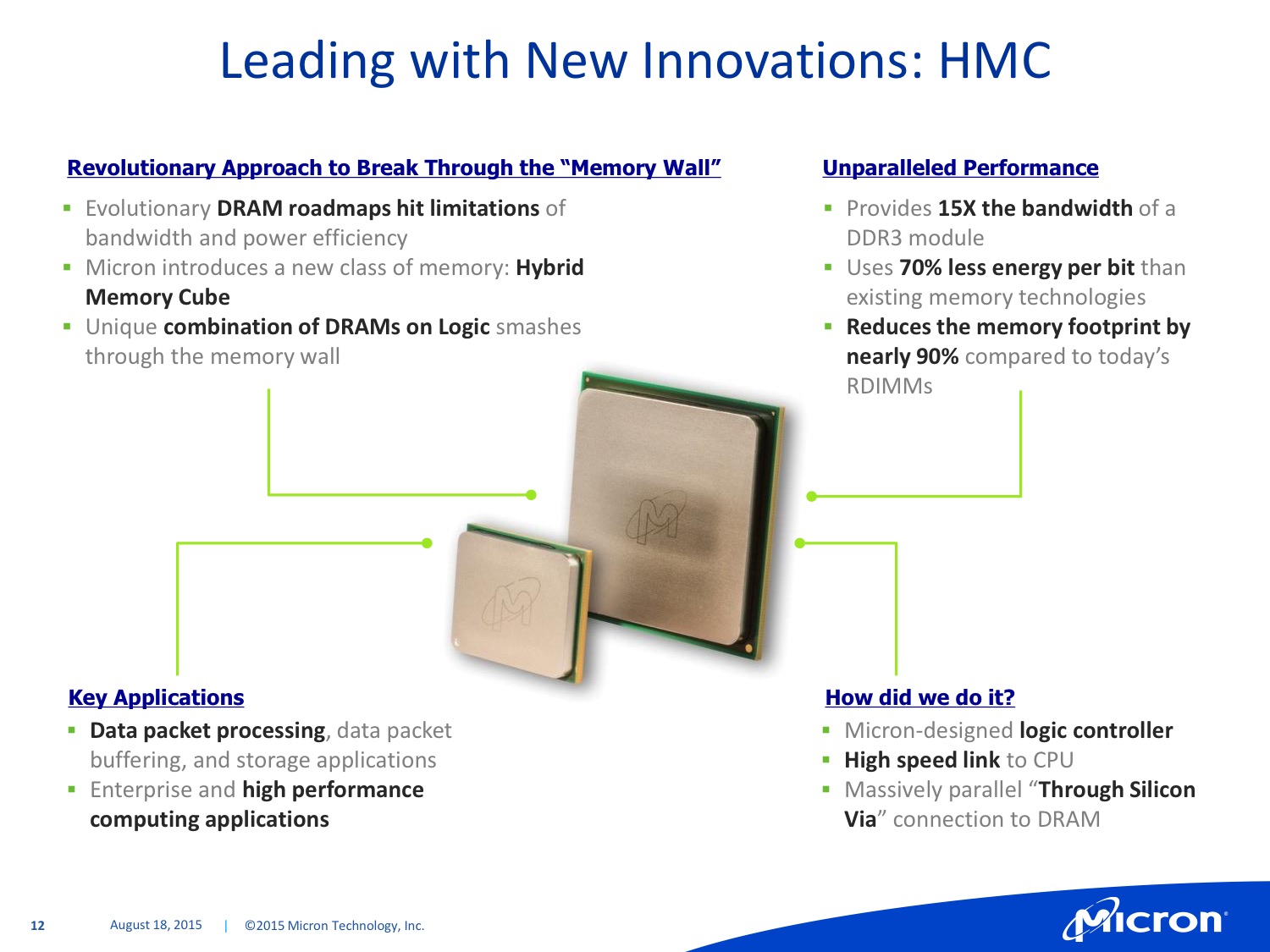

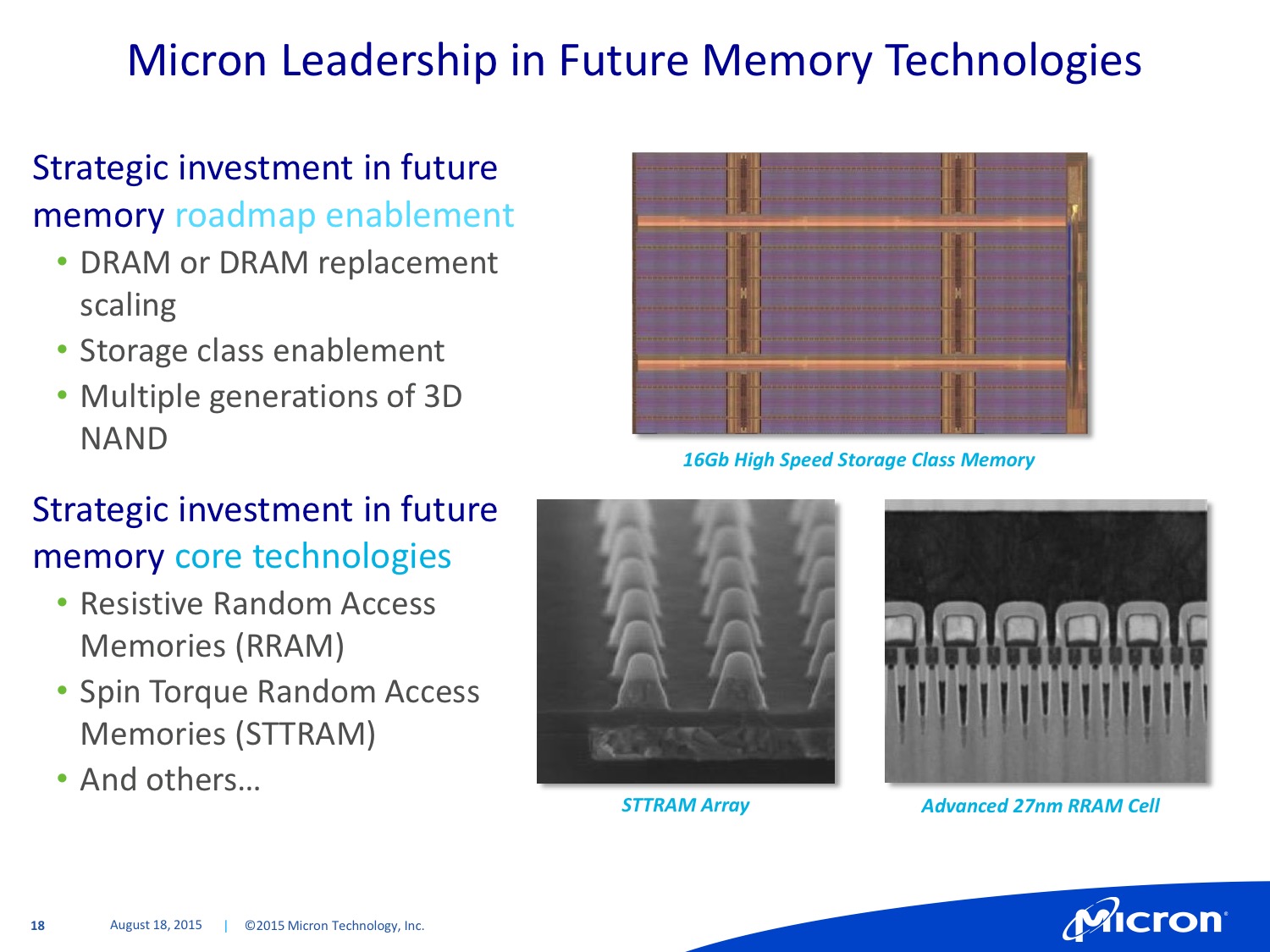

La société a également effectué une présentation ou elle a évoqué ses technologies mémoires. Le constructeur continue de travailler sur l'Hybrid Memory Cube (HMC), une technologie qui supperpose des dies de mémoires avec une couche de contrôleurs logiques. La troisième génération est en cours de développement même si l'on ne sait pas encore ce qu'elle apportera.

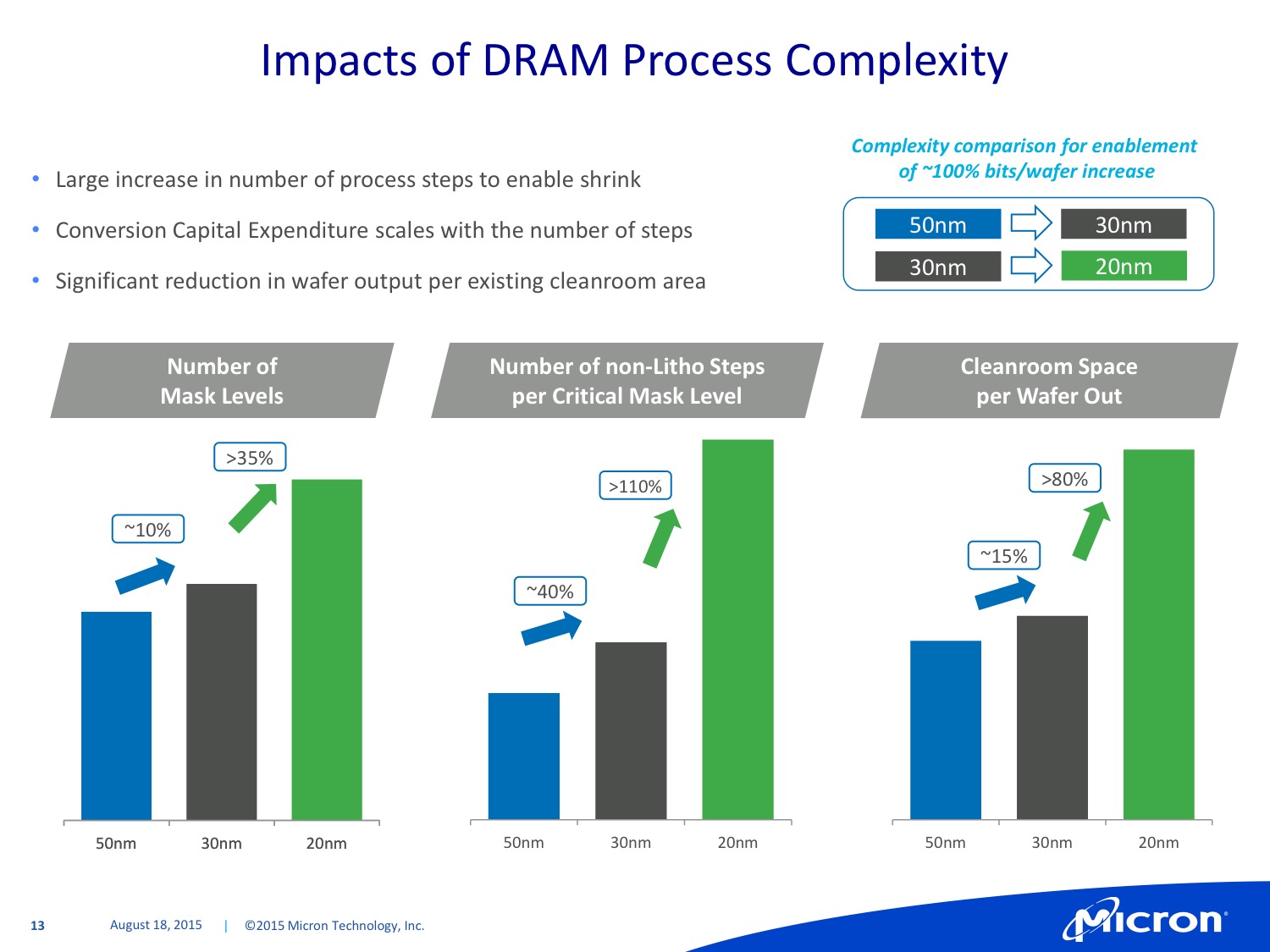

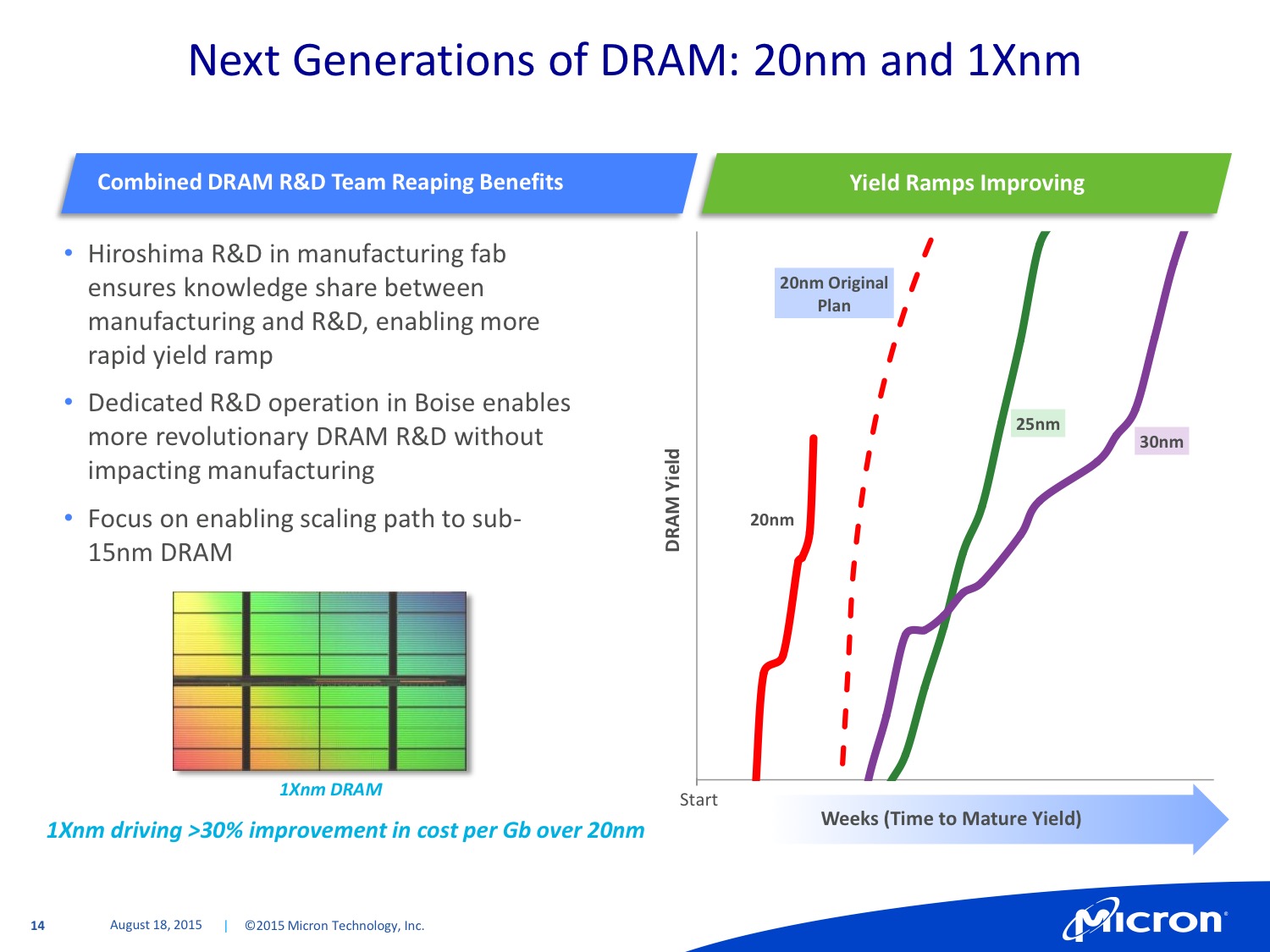

Micron est également revenu sur la complexité de la fabrication de la mémoire DRAM a 20nm et au dela. L'augmentation des coûts via les masques et les opérations rend de plus en plus difficile chaque passage à un nouveau node. Malgré tout le fabricant s'est felicité de ses yields atteint en 20nm et a indiqué travailler sur le 15nm et au delà.

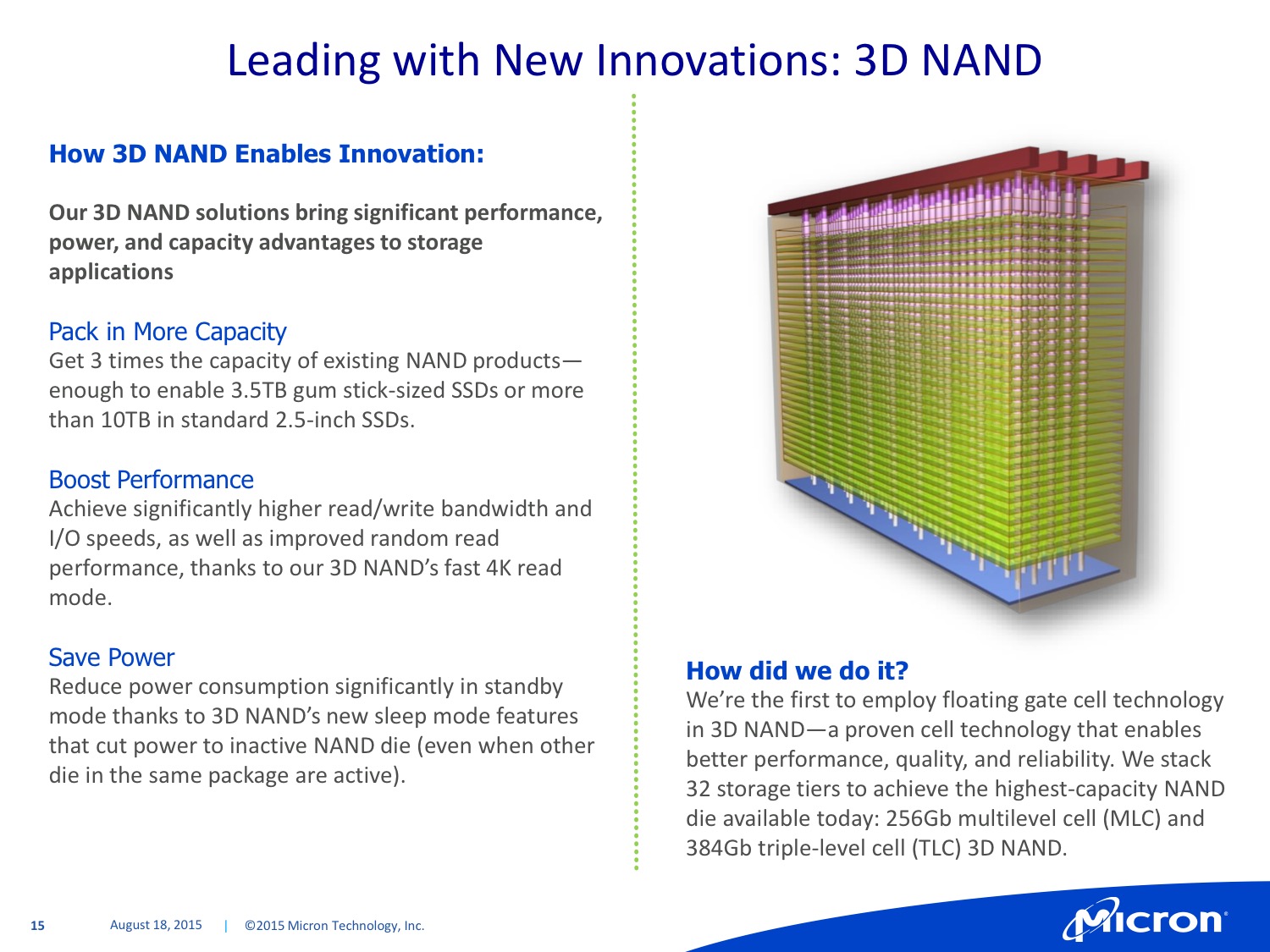

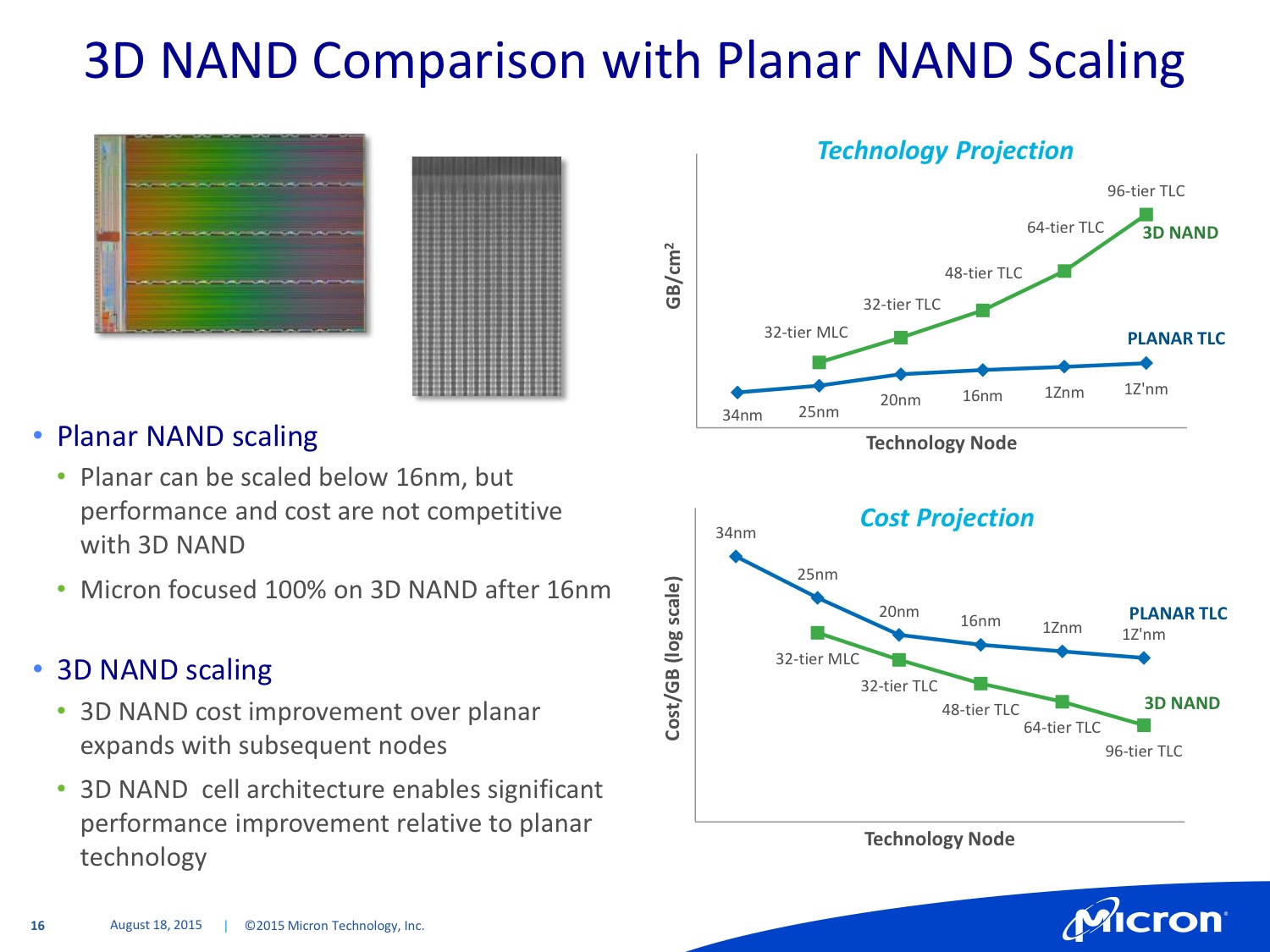

Côté NAND, Micron a confirmé que le 16nm serait son dernier node « traditionnel » et qu'il passait au delà à une gamme 100% 3D NAND. Cette variante de la NAND permet pour rappel de construire les cellules verticalement pour les empiler en augmentant la densité. Un avantage important qui permet d'utiliser des process plus anciens, et mieux maitrisés, autour de 50nm pour la première génération de Micron. La seconde génération de 3D NAND apparaitra en 2016.

3D XPoint a été peu évoqué, si ce n'est sur le fait qu'il y aura une seconde génération de cette mémoire en 2016. On notera que Micron parle toujours sur ses roadmaps d'une seconde nouvelle mémoire qui arriverait en 2017. Une variante de STTRAM (Spin Transfer Torque RAM) semble être l'une des possibilités, il faudra attendre un peu avant d'en savoir plus !