IDF: Haswell : premiers détails !

Publié le 12/09/2012 à 00:30 par Guillaume Louel

Si la Keynote n'a pas été l'occasion de grandes annonces, les sessions techniques de l'IDF sont toujours beaucoup plus riches en détails ! Une première session de la matinée était dédiée à l'architecture d'Haswell, celle qui prendra place dans les remplaçants d'Ivy Bridge.

D'abord dans les grandes lignes, trois versions seront disponibles. Outre la version desktop et mobile, une version spécifique deux coeurs dédiée aux ultrabook sera également au programme. Différence principale avec la version mobile, elle intégrera (au sein du package) directement le chipset, pour un TDP de 15 watts (Intel n'ayant pas précisé si la version sous les 10 watts dont nous parlions précédemment intègrera également le chipset).

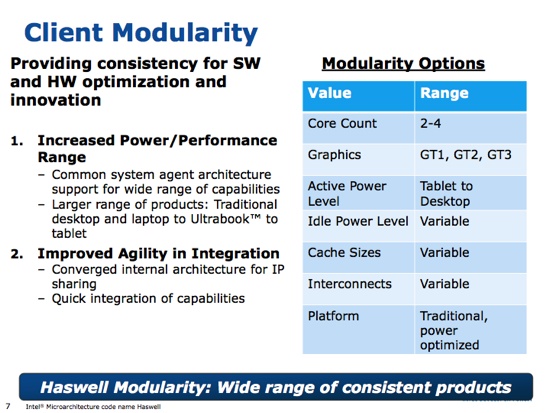

La modularité est le maitre mot utilisé par Intel pour Haswell. Outre le nombre de cores qui variera de deux à quatre, on trouvera trois coeurs graphiques distincts.

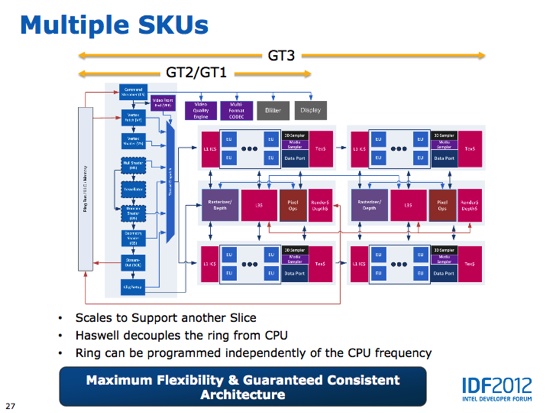

La nouveauté vient de l'arrivée de GT3, une troisième option graphique qui double ce qu'Intel appelle le slice. On trouvera donc deux blocs de rasterisation, de Z, de Stencil et de blending en plus des unités de calculs doublées. La partie en amont du GPU a été redimensionnée en fonction pour pouvoir gérer ces blocs supplémentaires. La présence du bloc mémoire additionnel a été éludée dans la présentation.

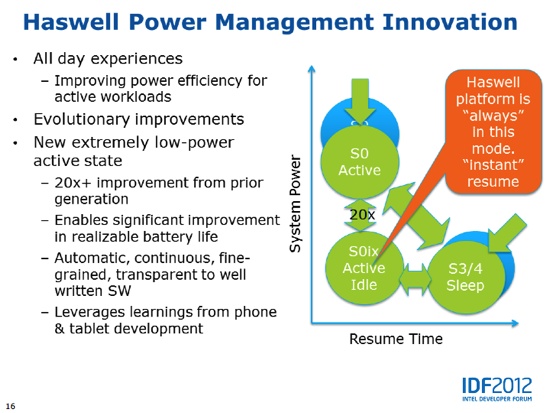

Du côté de la gestion de l'énergie, la plateforme gère les états SOix (1, 2 et 3) notamment supportés par Microsoft pour Windows 8 sous le nom de Connected Standby . L'intérêt de ces états est de proposer une plus grande finesse dans la gestion de l'économie d'énergie avec la possibilité de sortir de ces modes de veille avancés en 100 micro secondes, 3 milli secondes et 300 milli secondes (pour SOi 1, 2 et 3 respectivement).

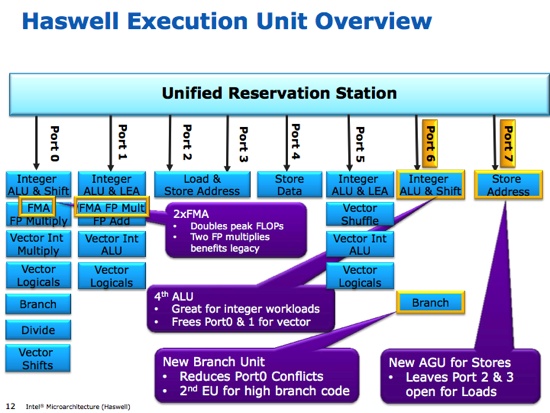

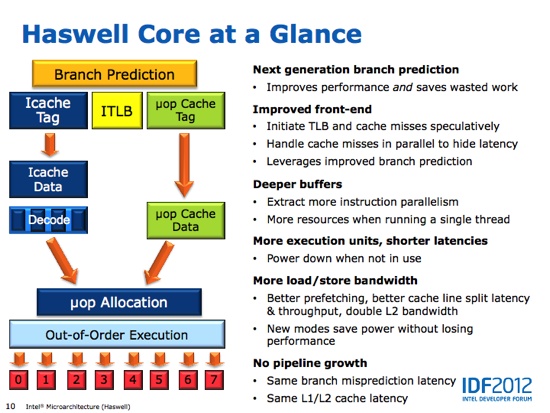

Comme nous l'indiquions précédemment, Intel a effectué quelques changements dans son architecture CPU. D'abord du côté des instructions par cycles, deux ports sont ajoutés ce qui permet au moteur OoO de traiter jusque 8 instructions par cycle. Deux ports peuvent être utilisés pour les instructions FMA (A=A+BxC en virgule flottante), doublant leur capacité théorique de traitement.

Les modifications ne s'arrêtent pas là avec des changements (non documentés) sur l'unité de prédiction de branchements et une augmentation de la taille de multiples buffers.

Intel est revenu sans plus de précisions sur le support de la mémoire transactionnelle, avec TSX. Nous avions pour rappel parlé de cette technologie en détails dans cet article. D'autres détails devraient être dévoilés dans des sessions techniques sur lesquelles nous reviendrons bientôt.

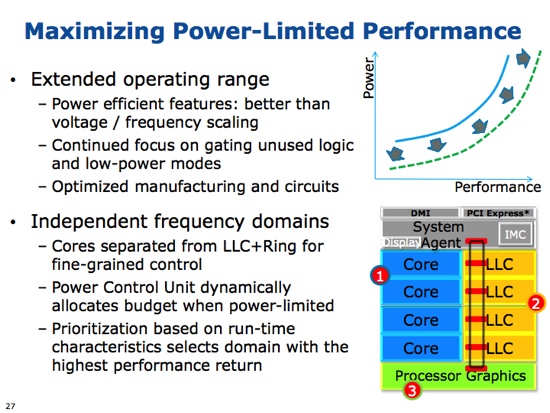

Dernier point notable au niveau de la PCU, Intel indique que le ring bus et la mémoire cache font désormais partie d'un plan d'alimentation complètement séparé.

Des premiers détails plutôt alléchants pour ces puces. Leur arrivée étant toujours prévue pour le second trimestre 2013.

Vos réactions

Contenus relatifs

- [+] 07/02: Windows 10, Meltdown et Spectre : q...

- [+] 26/03: Nouveaux Pentium et Core i3 Haswell...

- [+] 01/10: Perfs avec 2, 4, 6 et 8 curs : 4 j...

- [+] 29/08: Intel Haswell-E, LGA 2011-v3 et DDR...

- [+] 12/08: Intel désactive TSX suite à un bug

- [+] 21/07: +100 MHz pour +0$ sur les Core i3 e...

- [+] 23/06: i3-4370, i3-4160 et Pentium G3460 e...

- [+] 17/06: ASUS permet l'oc du G3258 sur toute...

- [+] 13/06: Core i7-4790K en test, Devil's Cany...

- [+] 11/06: EUs des iGPU Broadwell et Skylake