IDF: Haswell : retour sur la partie graphique

Publié le 12/09/2012 à 17:48 par Guillaume Louel

En plus de ce que nous indiquions ce matin, nous avons glanés quelques détails supplémentaires sur la partie graphique intégrée à Haswell

D'abord au niveau du support des écrans. A l'image d'Ivy Bridge, trois framebuffers distincts sont gérés dans la puce pour piloter jusque trois écrans. Une possibilité qui réclame que deux ports DisplayPort soient présents sur la carte mère (voir notre test d'Ivy Bridge pour plus de détails) et qui n'est en pratique pas exploitée.

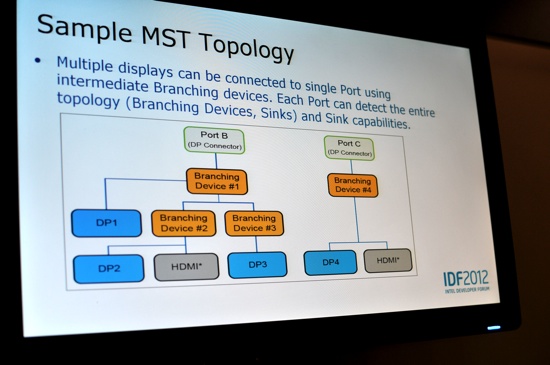

Haswell améliorera un peu la situation en supportant officiellement les hubs Display Port (MST pour Multi Stream Transport). Une démonstration d'Intel nous a montré l'utilisation de trois écrans simultanés connectés via trois hubs 2 ports chainés les uns aux autres (en pratique deux hubs 2 ports auraient suffit, Intel mettait simplement en avant pour sa démonstration sa gestion du chainage).

Sur ce schéma, on peut voir l'exemple d'une carte mère ou six écrans (4 DP et 2 HDMI)sont connectés sur deux ports Display Port. Attention cependant : s'il est possible de connecter plus de trois écrans, en pratique seuls trois images distinctes peuvent être générées côté GPU. Intel met simplement en avant avec ce schéma la possibilité d'effectuer du mirroring. Intel n'est pas le premier a gérer le support des hubs MST, AMD par exemple le propose depuis les HD 6000. Seul problème, ces hubs sont encore aujourd'hui introuvables. Rayon d'espoir sur ce point : selon notre interlocutrice, le modèle utilisé (basé sur un contrôleur ST Micro) pour la démonstration sera réellement disponible avant la fin du mois !

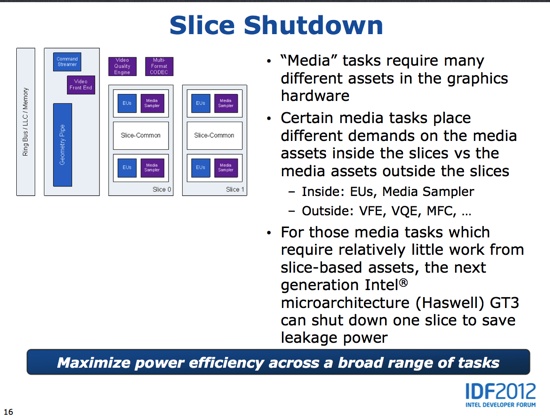

Terminons avec quelques détails supplémentaires sur les coeurs graphiques proprement dits. D'abord, une des particularités de la version GT3 de l'IGP est qu'elle dispose de deux partitions indépendantes, Intel les appelle «slice». L'intérêt de ce découpage est que dans le cas d'une charge graphique «légère», Haswell peut désactiver complètement l'un de ses slices pour limiter la consommation, une fonctionnalité qui a été ajoutée dixit le présentateur de la conférence pour les Ultrabook. Une confirmation du fait que l'on devrait retrouver ce GT3 dans des SKUs mobiles !

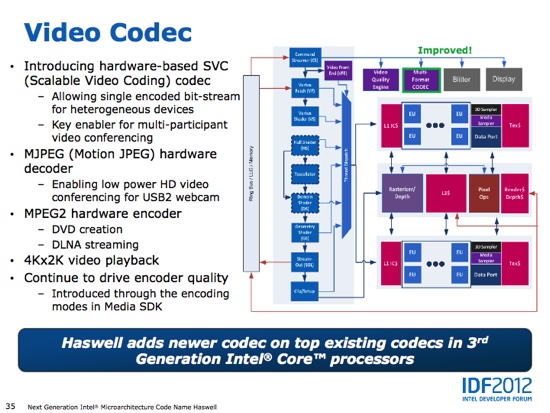

Enfin, Intel a ajouté quelques détails sur la partie codec de son IGP. On trouve quelques ajouts qui visent principalement l'accélération de la vidéo conférence. D'abord, l'encodeur H.264/AVC (connu sous le terme marketing QuickSync, voir ici) gère désormais la version «Scalable» du format. Il s'agit d'une extension du H.264 adaptée à la transmission de vidéo en ligne qui rajoute une notion de robustesse, le format peut en effet continuer a décoder une version dégradée de la vidéo en cas de fluctuation de la bande passante par exemple. Deux autres formats sont également gérés, le MPEG2 en encodage et le MJPEG en décodage. Dans les trois cas, le but est le même : ces formats serviront à accélérer des applications de type vidéo conférence (avec la possibilité d'améliorer le streaming également dans le cas du SVC).

Vos réactions

Contenus relatifs

- [+] 07/02: Windows 10, Meltdown et Spectre : q...

- [+] 26/03: Nouveaux Pentium et Core i3 Haswell...

- [+] 01/10: Perfs avec 2, 4, 6 et 8 curs : 4 j...

- [+] 29/08: Intel Haswell-E, LGA 2011-v3 et DDR...

- [+] 12/08: Intel désactive TSX suite à un bug

- [+] 21/07: +100 MHz pour +0$ sur les Core i3 e...

- [+] 23/06: i3-4370, i3-4160 et Pentium G3460 e...

- [+] 17/06: ASUS permet l'oc du G3258 sur toute...

- [+] 13/06: Core i7-4790K en test, Devil's Cany...

- [+] 11/06: EUs des iGPU Broadwell et Skylake