Les contenus liés aux tags 16/14nm et 10nm

Afficher sous forme de : Titre | Flux16nm en 2013, 10nm EUV en 2015 chez TSMC

Résultats Intel en baisse, perspectives 2013

16nm en 2013, 10nm EUV en 2015 chez TSMC

Nos confrères d'EE Times ont publié le résumé d'une présentation par TSMC de ses nodes à venir, un article dans lequel on peut relever quelques informations intéressantes.

TSMC revient d'abord rapidement sur l'état de son node 28nm. Sa Gigafab 15 produirait aujourd'hui 50000 wafers dans ce node par mois. Cette quantité devrait cependant rapidement doubler avec la mise en route de la seconde tranche de la Gigafab 15. La production devrait démarrer d'ici un mois et arriver, d'ici cinq mois, à un débit de production identique à la première tranche.

En ce qui concerne le 20nm, TSMC donne quelques détails intéressants. Avec l'arrivée du double patterning sur ce node, les gains habituels de densité et de performances devraient être réduits, une tendance que l'on avait déjà entendue du côté de la Common Platform. Le 20nm sera vraisemblablement un node de transition vers le FinFET (le node suivant en 16nm), même si TSMC se refuse de le dire. Côté performances, quelques chiffres ont été donnés à savoir 20% de fréquence en plus, ou 30% de consommation en moins par rapport au 28nm, ce qui reste tout de même assez élevé. Une vingtaine de tapeouts sont attendus cette année dans les Gigafab 12 et 14 avec une production en volume pour 2014. Parmi ceux-ci, un Cortex-A15 20nm est attendu pour le mois de mai.

Pour le 16nm, le développement du node est actuellement en cours en parallèle, on se souvient de cette annonce en début de mois d'un premier tapeout de Cortex-A57. Assez peu de détails sont donnés, si ce n'est que les premiers wafers de tests clients pourraient être lancés vers la fin de l'année avec une production qui monterait (probablement très doucement) en volume en 2014. Actuellement, TSMC travaille principalement sur des structures SRAM 128 Mbit dont les yields sont en avance par rapport aux estimations. Si les blocs logiques ont déjà été testés (cf l'annonce du Cortex), les blocs d'interface (mémoire ou autre) devraient commencer à être testés en juin.

De manière beaucoup plus surprenante, TSMC à indiquer espérer produire d'ici 2015 des wafers 10nm utilisant la technologie EUV. Pour rappel, TSMC a investit également dans le fournisseur d'outils ASML.

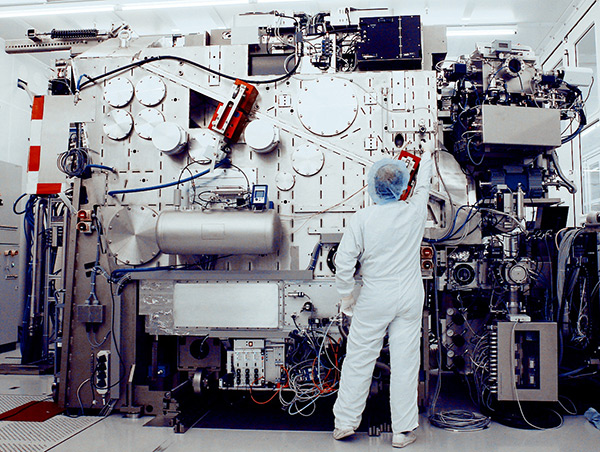

Une machine EUV ASML

La firme se réserve cependant assez prudente, indiquant qu'elle ne dispose toujours pas du dernier modèle d'outil de ASML (le NXE:3300 ). TSMC indique également continuer a travailler sur une technologie alternative pour ce node, le multiple electron beams sur lequel TSMC avait annoncé travailler avec MAPPER . La particularité de la technologie est qu'il ne s'agit plus littéralement de photolithographie, le masque disparaît et la source lumineuse est remplacée par des flux d'électrons qui viennent réagir avec un film préalablement déposé sur le wafer. Le débit de ces machines est qualifié par TSMC "d'encore trop lent", même s'il n'est pas comparé à celui, lui aussi très lent, de la technologie EUV actuellement (nous vous renvoyons a cette interview ou Mark Bohr évoquait le problème).

On notera enfin quelques informations sur les technologies de die stacking et les progrès en matière de 2.5D et 3D. Le concept du die stacking consiste à relier plusieurs dies directement entre eux par une couche de silicium, sans nécessiter de fils (des TSVs, Through Silicon Vias, sont utilisésà la place, ce qui permet d'augmenter significativement la bande passante et réduire la complexité). Les technologies dont on parle visent à terme à relier plusieurs dies logiques entre eux même si ce n'est pour l'instant qu'un objectif lointain.

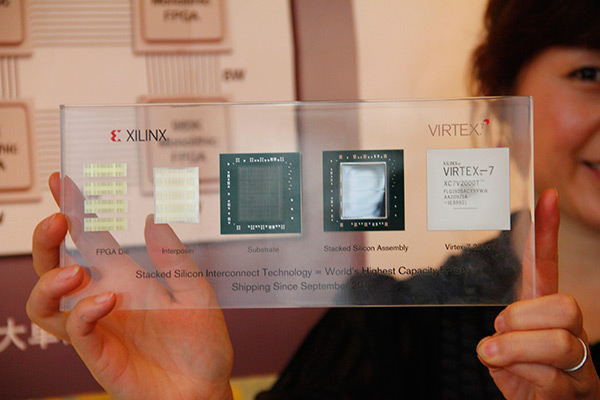

La technologie 2.5D consiste à placer côte a côte deux dies, qui reposent sur un interposer qui contient lui-même des TSV pour interconnecter les dies. L'épaisseur de cet interposer est actuellement de 100nm mais devrait se réduire de moitié. Xilink propose actuellement un FPGA fabriqué sur le process 28HPL de TSMC qui interconnecte quatre dies, le Virtex 7 2000T.

Sur cette photo de nos confrères de 52solution , vous pouvez voir à gauche les quatre dies logiques et l'interposer. La puce assemblée est en quatrième position.

TSMC indique que les yields obtenus dépassent les 95% sur les interposers utilisés pour cette puce et plusieurs autres tape-outs devraient avoir lieu cette année, sans plus de précision. TSMC continue de travailler sur le sujet de Wide I/O avec des puces de test qui lient un die 40nm avec une puce mémoire Hynix, un montage qui a passé les tests de validation du JEDEC.

En ce qui concerne la superposition de dies (la "vraie" 3D), TSMC pense effectuer le tapeout d'une puce 28nm avec sur chaque couche des dies mémoire, avant de passer au mélange logique/mémoire. Il faudrait cependant attendre 2015 ou 2016 pour retrouver ces puces en production selon TSMC.

Notons enfin qu'en ce qui concerne le 450mm (la taille des wafers, elle est actuellement de 300mm de diamètre pour les nodes haut volume de TSMC), la production ne devrait pas démarrer au mieux avant 2016 voir 2017 malgré des tests en cours. Les outils EUV sont ceux qui poseront - là encore- le plus de problème selon TSMC, ils pourraient ne pas arriver avant 2017 en version 450mm.

Résultats Intel en baisse, perspectives 2013

Intel vient d'annoncer un chiffre d'affaires de 13,5 milliards de $ pour un bénéfice net de 2,5 milliards de $ pour son dernier trimestre 2012. Ces résultats feraient rêver de nombreuses entreprises mais ils sont décevants pour Intel, en forte baisse par rapport au dernier trimestre 2011.

Intel vient d'annoncer un chiffre d'affaires de 13,5 milliards de $ pour un bénéfice net de 2,5 milliards de $ pour son dernier trimestre 2012. Ces résultats feraient rêver de nombreuses entreprises mais ils sont décevants pour Intel, en forte baisse par rapport au dernier trimestre 2011.

Les ventes sont en effet en baisse de 3%, et surtout le bénéfice net baisse de 27% du fait d'une marge brute qui est à 58%, contre 64,5% il y a un an. Du fait d'un bon début d'année, les chiffres globaux de 2012 sont meilleurs avec 53,3 milliards de chiffres d'affaires et 11 milliards de bénéfices, soit 1,2% et 15% de moins que 2011. La marge brute est à 62,1%, en baisse de 0,4 points.

Dans le détail les ventes de la division PC Client (desktop/mobile) sont en baisse de 6% sur le dernier trimestre par rapport à l'an passé, contre 4% de mieux pour la division Data Center (serveurs), 7% de moins pour la division Other Intel Architecture (solutions embarquées et Atom) et 16,9% de mieux pour le Software and Services Group (McAfee entre autre). Les ventes respectives de ces divisions sont de 8506, 2830, 1018 et 636 millions de $ sur le trimestre.

Sur l'année 2012 Intel note une hausse des volumes de 2% sur ses ventes destinées aux Notebook, mais avec un prix de vente moyen en baisse de 6% par rapport à 2011. Côté destkop le prix moyen a augmenté de 4% mais le volume a baissé de 5%.

Pour l'année 2013, Intel s'attends à une hausse de son volume des ventes comprise entre 1 et 5%, pour une marge brute d'environ 60%. Les investissements devraient être portés à 13 milliards de $, contre 11 milliards en 2012. 2 milliards de $ seront dédié à la construction d'une première usine travaillant sur des wafer de 450mm, et une partie de 11 milliards restant iront à la montée en puissance de la production en 14nm ainsi qu'au développement du 10nm.

Côté produit le géant de Santa Clara a confirmé à l'occasion de l'annonce de ses résultats le lancement d'Haswell, qui est déjà en production, au premier semestre, puis de Xeon mais aussi d'Atom gravés en 22nm destinés aux serveurs. Intel a également parlé des premières livraisons du SoC Atom 22nm Valleyview et des plates-formes Bay-trail aux OEM, ainsi que du lancement de la production en 14nm en fin d'année 2013.