Les contenus liés aux tags Samsung et Micron

3D NAND 48 couches chez Toshiba

Hybrid Memory Cube Gen2 en développement

Un consortium pour l'Hybrid Memory Cube

3D NAND 48 couches chez Toshiba

Toshiba vient d'annoncer avoir produit des puces mémoires flash (NAND) à construction verticale (souvent appelée 3D NAND) à 48 couches. Pour rappel, en 2007 Toshiba avait été le premier à produire une technologie de mémoire ou l'organisation des cellules se fait non plus de manière horizontale comme traditionnellement, mais cette fois ci de manière verticale.

La mémoire NAND traditionnelle au milieu en haut peut être empilée (Stack), la stratégie classique que l'on voit à droite, ou bien transposée verticalement (le chemin de gauche) pour réaliser une structure appelée BiCS par Toshiba qui peut être vue comme le pendant du FinFET pour la NAND

En 2007, Toshiba ne précisait pas le nombre de couches qu'il avait réussi à superposer dans sa structure mais évoquait dans son communiqué de presse le nombre de 32 pour expliquer les difficultés de l'empilement. Presque huit années après, le constructeur indique aujourd'hui avoir produit des puces 48 couches de 128 Gbits (16 Go) qui sont disponibles dès aujourd'hui sous la forme d'échantillons.

Toshiba indique également qu'il commercialisera cette mémoire à partir de 2016, elle sera fabriquée en volume dans la nouvelle Fab2 située à Yokkaichi au Japon. En 2014, Toshiba avait annoncé remplacer cette ancienne usine par une nouvelle qui serait capable de produire de la mémoire NAND classique et « 3D » à compter de 2016. Le communiqué de la marque indique que la Fab2 devrait être opérationnelle durant la première moitié de 2016.

Cette structure de mémoire permet théoriquement d'augmenter fortement la densité même si pour l'instant, il faut se contenter de puces 128 Gbits pour ce premier échantillon. On rappellera que si Toshiba a été pionnier de cette technologie, Samsung avait été le premier à lancer la production de sa propre version de mémoire NAND verticale, baptisée V-NAND en 2013. Si l'agencement technique semblait légèrement différent du BiCS de Toshiba (voir notre article), le principe de base reste le même.

Cette V-NAND s'est ainsi retrouvée dans les SSD 850 Pro du constructeur sous la forme de puces empilant 32 couches. De son côté, si Toshiba met en avant l'empilement de 48 couches, on ne connait pas encore la finesse de gravure qui sera utilisée. Plus de détails seront probablement dévoilés d'ici à l'année prochaine. Pour le reste de la concurrence, Intel et Micron devraient proposer leur version 3D NAND 32 couches au second semestre 2015, tandis qu'il faudra attendre 2016 pour Hynix.

Hybrid Memory Cube Gen2 en développement

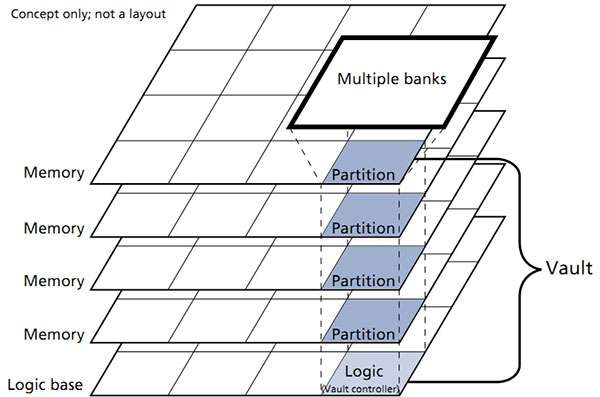

L'Hybrid Memory Cube Consortium (fondé par Micron et Samsung en 2011, rejoint ensuite par Hynix et 120 sociétés donc ARM, IBM, Microsoft et Xilinx) vient de publier un communiqué indiquant le développement d'une seconde génération de cette mémoire. Pour rappel, le concept de l'HMC est de superposer plusieurs dies de mémoire DRAM par-dessus une die de logique, le tout étant relié par des TSV (Through Silicon Vias, des fils qui traversent les dies).

Nous avions parlé un peu plus en détail de la première version de cette spécification en septembre dernier, nous vous renvoyons vers cet article si vous souhaitez plus de détails.

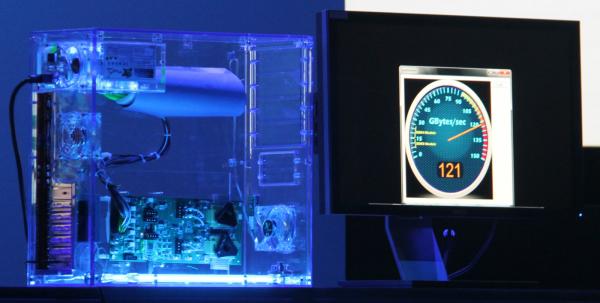

La nouvelle spécification est encore au statut de « draft » (en préversion) et n'a été pour l'instant partagé qu'avec les membres du consortium dans le but d'être finalisé en mai 2014. La nouvelle version de la spec évoque des augmentations de bande passante, en doublant à 480 Go/s la bande passante totale des puces pour le modèle 4 liens, et 480 Go/s également pour le modèle huit liens (contre 320 dans la spec version 1.0).

Si Samsung et Hynix sont impliqués dans le développement du standard, Micron reste pour l'instant le seul constructeur à avoir produit des échantillons commerciaux.

Un consortium pour l'Hybrid Memory Cube

Démontrée par Intel et Micron lors de l'IDF, la technologie Hybrid Memory Cube s'ettoffe un peu aujourd'hui avec l'arrivée de Samsung. Micron et Samsung ont en effet annoncé la création d'un consortium dédié à cette technologie dans le but de développer une spécification commune pour l'industrie. Une préversion de la spécification devrait être partagée sous peu par le consortium afin de recueillir suggestions et remarques. La version finale est annoncée pour 2012.

Pour rappel, l'Hybrid Memory Cube consiste à superposer plusieurs die de mémoire DRAM avec un die logique (le processeur). Le prototype présenté lors de l'IDF disposait d'une bande passante de 128 Go/s obtenus avec quatre die DRAM qui communiquent directement avec la couche logique par le biais d'interconnexions qui traversent les die (through-silicon vias).