Les derniers contenus liés aux tags DDR4 et JEDEC

Le JEDEC publie (enfin !) la spec. DDR4

Attendue dans un premier temps fin 2011, puis pour la mi 2012, c'est finalement mardi dernier que le JEDEC - le consortium des différents acteurs de l'industrie informatique qui détermine les standards mémoires - a publié la spécification de ce qui sera le prochain standard mémoire de nos machines : la DDR4. Comme nous l'indiquions précédemment, là ou l'écart entre la publication de la DDR, DDR2 et DDR3 avait été entre chaque de quatre années, il aura fallu plus de sept ans entre la publication de la spécification de la DDR3 et celle de la DDR4.

Une longévité fortement accrue et qui s'est traduite par l'arrivée de barrettes qui dépassent très largement les objectifs d'origines de la DDR3 : on voit des modèles annoncés au-delà de la DDR3-2600 quand la spécification de la DDR3 ne validait officiellement les modules ne montant que jusqu'à 1600 (à l'origine, la spécification ayant été modifiée pour aller jusque 2133). Le JEDEC, qui n'aimait en général pas particulièrement ces dépassements (qui avaient existés auparavant, on se souvient par exemple de la DDR2-1066 là ou 800 était le maximum autorisé) à d'ailleurs fermé les yeux sur ces barrettes même si le communiqué reconnait que la DDR3 à "dépassé ses objectifs originaux de performances" et qu'il est probable que la DDR4 fasse de même.

Nous avions déjà évoqué dans une actualité précédente quelques unes des grandes lignes techniques qui devaient être utilisées pour la DDR4, à savoir l'utilisation de transferts de largeurs variables (32, 64 ou 128 bits effectifs par transfert au lieu de 64 uniquement pour la DDR3) ou l'implémentation du concept DBI (Data Bit Inversion) qui permet de simplifier certains transferts en inversant les bits dans le but de limiter la consommation.

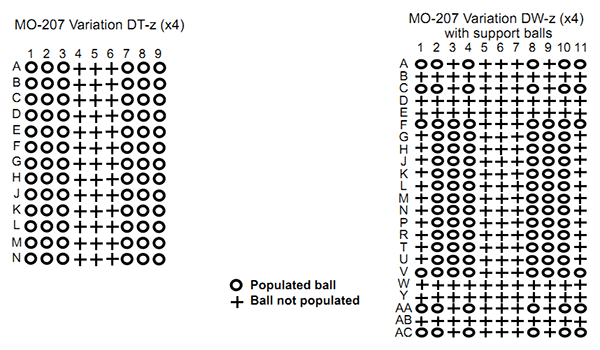

Version x4/x8 classique à gauche et version x16

L'organisation de l'adressage évolue avec l'apparition de groupes de banques indépendants les un des autres au sein puces. On trouve ainsi 2 groupes de 4 banques sur les puces x16 et 2 groupes de 4 banques sur les puces x16,, une nouveauté qui est à la base de l'amélioration des débits.

D'autres petits détails sont présents comme l'adaptation à la température de la puce qui doit pouvoir au minimum supporter 85°, un mode additionnel de fonctionnement jusqu'à 95° est également présent, dans ce cas les puces mémoires forceront un rafraichissement des données plus régulier pour éviter toute perte d'information (et plantage). Un mode de rafraichissement plus lent (période plus longue entre deux opérations) est également prévu pour un fonctionnement sous les 45°.

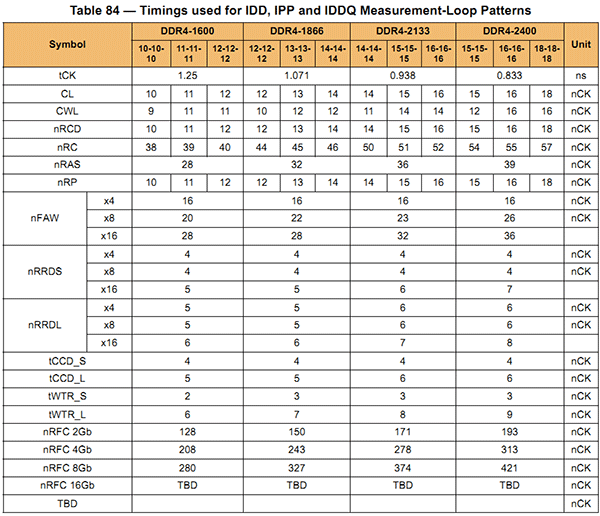

Du côté des débits, la DDR4 démarrera officiellement avec la DDR4-1600 (1600 MT/s) avec pour objectif d'atteindre 3200 MT/s d'ici à la fin de vie du standard. Les latences, exprimées en cycles paraitront forcément élevées même si l'on notera qu'elles sont assez proches de celles de la DDR3 actuelle (CAS 10 à 12 pour la DDR4-1600 au lieu de CAS9 couramment aujourd'hui pour la DDR3-1600). Ramenées en nanosecondes, ces latences restent très faibles et les multiples changements au niveau du fonctionnement interne font qu'il serait particulièrement faux de juger la DDR4 sur ces simples chiffres de latences.

Côté tensions, comme nous l'indiquions on passera de 1.5V à 1.2V pour la tension d'alimentation, sachant que des modules basse consommation (1.05V) sont également prévus (à l'image des barrettes DDR3 1.35V) sur le long terme. Une seconde tension de support à 2.5V (VPP) est également présente même si elle ne jouera qu'un rôle additionnel.

Nous nous devons enfin de noter que la spécification reste encore par endroit incomplète. Ainsi, si de manière normale certains timings ne sont pas encore définis au delà de 2400 MT/s, une (grande) partie de la spécification des timings électriques n'est pas du tout définie et ce pour toutes les fréquences de fonctionnement. Bien entendu cette première version de la spécification est amenée à évoluer d'ici à ce que les produits soient disponibles. La DDR4 est attendu pour rappel par Intel côté serveur pour 2014, et côté desktop pour 2015 au mieux comme nous l'indiquions ici .

Le JEDEC évoque la DDR4

![]() Le comité de standardisation dédié à la mémoire, le JEDEC, vient de publier quelques détails sur les pistes de travail empruntées pour le futur standard mémoire DDR4. La spécification est toujours en cours d'élaboration et le JEDEC annonce qu'elle devrait être terminée d'ici à mi-2012 (ce qui n'empêche pas des guerres d'annonces entre Samsung et Hynix

). C'est en soit un retard de plus puisque l'on attendait la finalisation de la spécification avant la fin de l'année. Si le nouveau délai est tenu, cela marquera sept années entre la publication des standards DDR3 et DDR4, là où quatre années séparaient les publications des standards DDR, DDR2 et DDR3.

Le comité de standardisation dédié à la mémoire, le JEDEC, vient de publier quelques détails sur les pistes de travail empruntées pour le futur standard mémoire DDR4. La spécification est toujours en cours d'élaboration et le JEDEC annonce qu'elle devrait être terminée d'ici à mi-2012 (ce qui n'empêche pas des guerres d'annonces entre Samsung et Hynix

). C'est en soit un retard de plus puisque l'on attendait la finalisation de la spécification avant la fin de l'année. Si le nouveau délai est tenu, cela marquera sept années entre la publication des standards DDR3 et DDR4, là où quatre années séparaient les publications des standards DDR, DDR2 et DDR3.

Si la tension d'alimentation principale de la mémoire devrait varier avec le temps (de 1.2 à 1.05V, de la même manière que la DDR3 aura évolué de 1.5 à 1.2V), la DDR4 imposera une tension pour les I/O (VDDQ) qui restera fixe quoiqu'il arrive, de 1.2V. Le but étant de simplifier les designs et d'assurer la compatibilité future plus facilement. La VDDQ jouera également un rôle dans le nouveau système de terminaison.

Afin de réduire la consommation et de limiter le bruit sur le bus, la DDR4 implémentera pour la première fois le concept du DBI (Data Bus Inversion). L'idée est de limiter au maximum les inversions complètes, par exemple passer d'une transmission de 1111 à 0000 puis de nouveau 1111. Via un bit supplémentaire, le DBI permet d'indiquer que la valeur du milieu doit être comprise comme inversée. En pratique ce sont donc des valeurs de 1111, 1111 et 1111 qui seront transmises. Le système avait déjà été intégré à la GDDR4 et 5, il évite dans tous les cas que plus de la moitié des valeurs changent entre deux transferts successifs.

Autre nouveauté notable, la largeur des transferts redevient variable. Si la DDR3 se limitait à des transferts d'une largeur de 64 bits (x8), la DDR4 rajoute un peu plus de flexibilité avec trois largeurs (32, 64, 128 bits).

La question de l'intégrité des transferts, généralement réglée de manière globale avec l'ECC se verra affublée d'un système supplémentaire de CRC qui pourra être utilisé ponctuellement, par exemple uniquement sur certaines opérations d'écritures. Un mécanisme de détection de la parité au niveau des puces est également prévu.

En ce qui concerne la gestion des canaux et les performances, le communiqué ne s'avance que très peu. La DDR4 à toujours pour objectif de doubler les transferts par broche par rapport à la DDR3 (de 0.8/1.86 GT à 1.6/3.2 GT). En ce qui concerne la topologie, s'il semblait acquis que le concept de canaux gérant plusieurs barrettes disparaisse au profit d'un modèle point à point (l'équivalent de multiples canaux ne gérant qu'une barrette à la fois, voir cette actualité), aucune précision supplémentaire n'a été apportée.

La prochaine réunion de travail du JEDEC se tiendra le 12 septembre.