Les derniers contenus liés aux tags IDF et Haswell

IDF: Haswell : retour sur la partie graphique

IDF: Haswell : premiers détails !

IDF: Haswell fonctionnel, en démo

IDF: La grand-messe Intel ouvre ses portes

IDF: Haswell : retour sur la partie graphique

En plus de ce que nous indiquions ce matin, nous avons glanés quelques détails supplémentaires sur la partie graphique intégrée à Haswell

D'abord au niveau du support des écrans. A l'image d'Ivy Bridge, trois framebuffers distincts sont gérés dans la puce pour piloter jusque trois écrans. Une possibilité qui réclame que deux ports DisplayPort soient présents sur la carte mère (voir notre test d'Ivy Bridge pour plus de détails) et qui n'est en pratique pas exploitée.

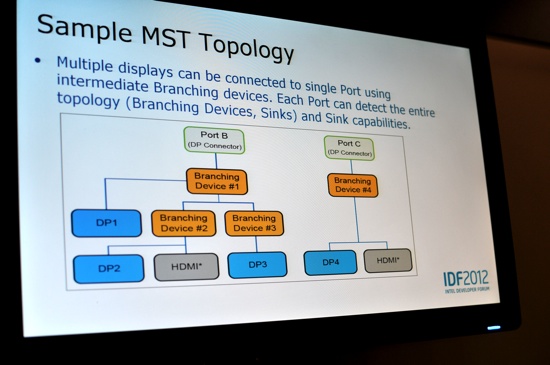

Haswell améliorera un peu la situation en supportant officiellement les hubs Display Port (MST pour Multi Stream Transport). Une démonstration d'Intel nous a montré l'utilisation de trois écrans simultanés connectés via trois hubs 2 ports chainés les uns aux autres (en pratique deux hubs 2 ports auraient suffit, Intel mettait simplement en avant pour sa démonstration sa gestion du chainage).

Sur ce schéma, on peut voir l'exemple d'une carte mère ou six écrans (4 DP et 2 HDMI)sont connectés sur deux ports Display Port. Attention cependant : s'il est possible de connecter plus de trois écrans, en pratique seuls trois images distinctes peuvent être générées côté GPU. Intel met simplement en avant avec ce schéma la possibilité d'effectuer du mirroring. Intel n'est pas le premier a gérer le support des hubs MST, AMD par exemple le propose depuis les HD 6000. Seul problème, ces hubs sont encore aujourd'hui introuvables. Rayon d'espoir sur ce point : selon notre interlocutrice, le modèle utilisé (basé sur un contrôleur ST Micro) pour la démonstration sera réellement disponible avant la fin du mois !

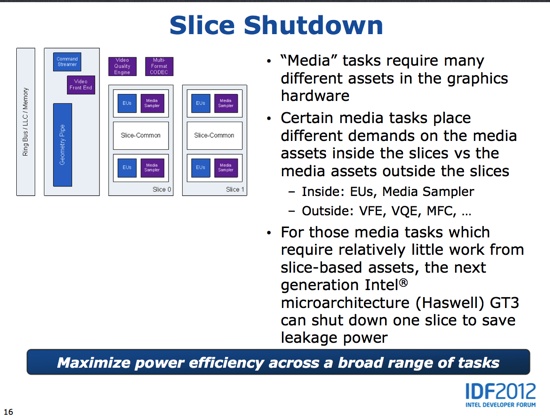

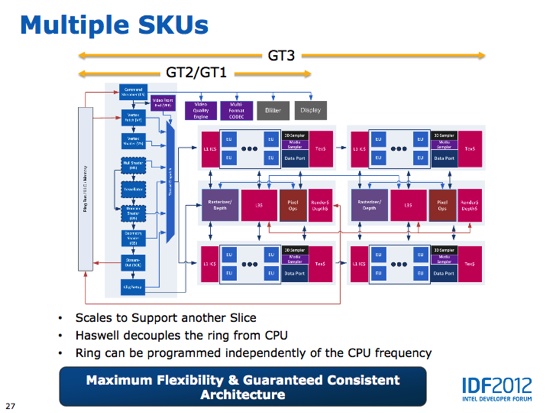

Terminons avec quelques détails supplémentaires sur les coeurs graphiques proprement dits. D'abord, une des particularités de la version GT3 de l'IGP est qu'elle dispose de deux partitions indépendantes, Intel les appelle «slice». L'intérêt de ce découpage est que dans le cas d'une charge graphique «légère», Haswell peut désactiver complètement l'un de ses slices pour limiter la consommation, une fonctionnalité qui a été ajoutée dixit le présentateur de la conférence pour les Ultrabook. Une confirmation du fait que l'on devrait retrouver ce GT3 dans des SKUs mobiles !

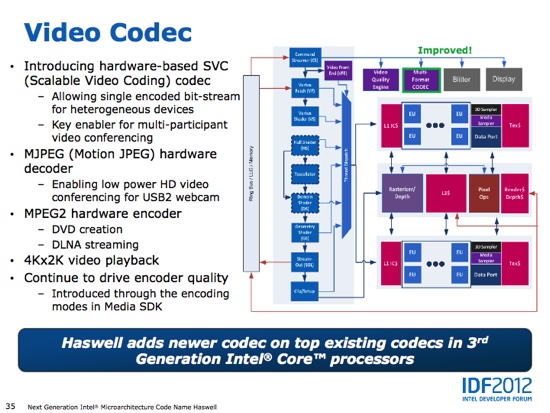

Enfin, Intel a ajouté quelques détails sur la partie codec de son IGP. On trouve quelques ajouts qui visent principalement l'accélération de la vidéo conférence. D'abord, l'encodeur H.264/AVC (connu sous le terme marketing QuickSync, voir ici) gère désormais la version «Scalable» du format. Il s'agit d'une extension du H.264 adaptée à la transmission de vidéo en ligne qui rajoute une notion de robustesse, le format peut en effet continuer a décoder une version dégradée de la vidéo en cas de fluctuation de la bande passante par exemple. Deux autres formats sont également gérés, le MPEG2 en encodage et le MJPEG en décodage. Dans les trois cas, le but est le même : ces formats serviront à accélérer des applications de type vidéo conférence (avec la possibilité d'améliorer le streaming également dans le cas du SVC).

IDF: Haswell : premiers détails !

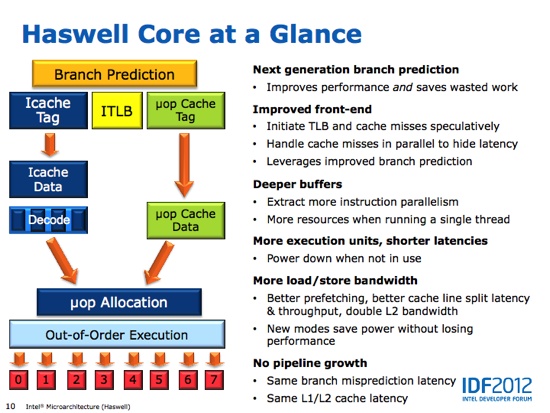

Si la Keynote n'a pas été l'occasion de grandes annonces, les sessions techniques de l'IDF sont toujours beaucoup plus riches en détails ! Une première session de la matinée était dédiée à l'architecture d'Haswell, celle qui prendra place dans les remplaçants d'Ivy Bridge.

D'abord dans les grandes lignes, trois versions seront disponibles. Outre la version desktop et mobile, une version spécifique deux coeurs dédiée aux ultrabook sera également au programme. Différence principale avec la version mobile, elle intégrera (au sein du package) directement le chipset, pour un TDP de 15 watts (Intel n'ayant pas précisé si la version sous les 10 watts dont nous parlions précédemment intègrera également le chipset).

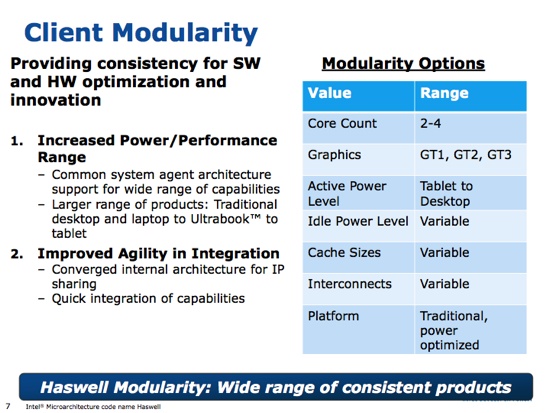

La modularité est le maitre mot utilisé par Intel pour Haswell. Outre le nombre de cores qui variera de deux à quatre, on trouvera trois coeurs graphiques distincts.

La nouveauté vient de l'arrivée de GT3, une troisième option graphique qui double ce qu'Intel appelle le slice. On trouvera donc deux blocs de rasterisation, de Z, de Stencil et de blending en plus des unités de calculs doublées. La partie en amont du GPU a été redimensionnée en fonction pour pouvoir gérer ces blocs supplémentaires. La présence du bloc mémoire additionnel a été éludée dans la présentation.

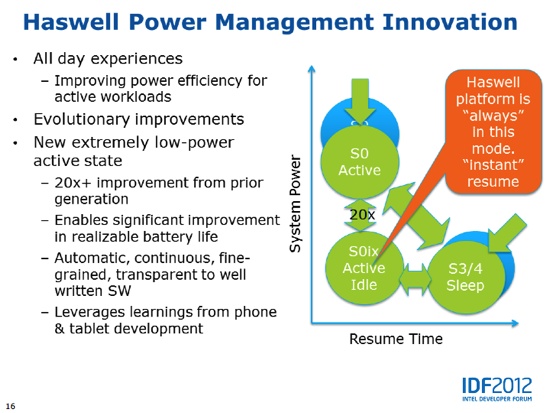

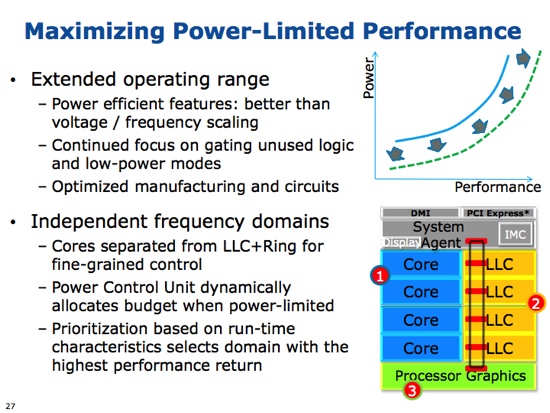

Du côté de la gestion de l'énergie, la plateforme gère les états SOix (1, 2 et 3) notamment supportés par Microsoft pour Windows 8 sous le nom de Connected Standby . L'intérêt de ces états est de proposer une plus grande finesse dans la gestion de l'économie d'énergie avec la possibilité de sortir de ces modes de veille avancés en 100 micro secondes, 3 milli secondes et 300 milli secondes (pour SOi 1, 2 et 3 respectivement).

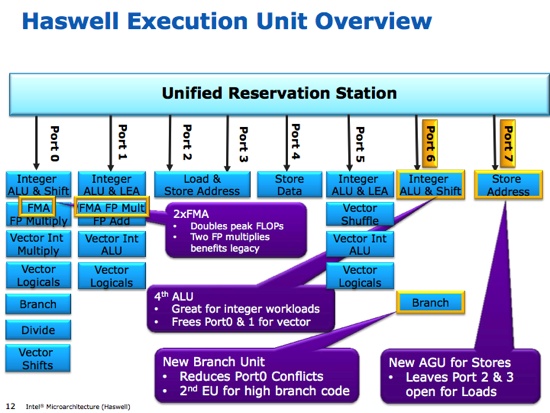

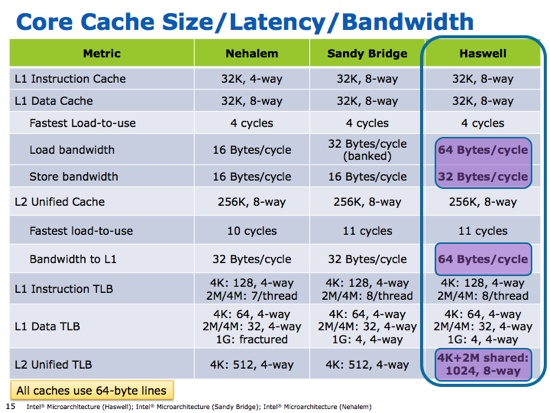

Comme nous l'indiquions précédemment, Intel a effectué quelques changements dans son architecture CPU. D'abord du côté des instructions par cycles, deux ports sont ajoutés ce qui permet au moteur OoO de traiter jusque 8 instructions par cycle. Deux ports peuvent être utilisés pour les instructions FMA (A=A+BxC en virgule flottante), doublant leur capacité théorique de traitement.

Les modifications ne s'arrêtent pas là avec des changements (non documentés) sur l'unité de prédiction de branchements et une augmentation de la taille de multiples buffers.

Intel est revenu sans plus de précisions sur le support de la mémoire transactionnelle, avec TSX. Nous avions pour rappel parlé de cette technologie en détails dans cet article. D'autres détails devraient être dévoilés dans des sessions techniques sur lesquelles nous reviendrons bientôt.

Dernier point notable au niveau de la PCU, Intel indique que le ring bus et la mémoire cache font désormais partie d'un plan d'alimentation complètement séparé.

Des premiers détails plutôt alléchants pour ces puces. Leur arrivée étant toujours prévue pour le second trimestre 2013.

IDF: Haswell fonctionnel, en démo

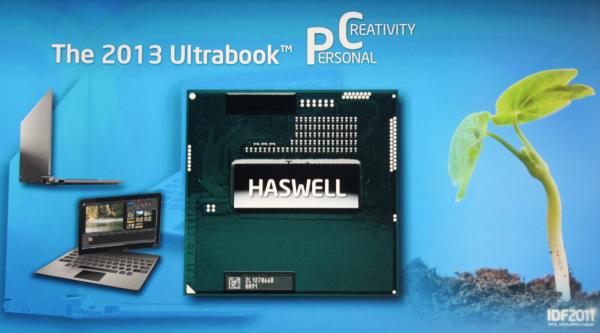

Après Ivy Bridge, Mooly Eden a voulu rassurer par rapport à l'avancement de la mise au point de son successeur, Haswell. Nous avons ainsi pu en apercevoir un prototype sur son packaging, laissant entrevoir un die au format très allongé, d'une taille assez proche de celui d'Ivy Bridge.

Intel a insisté une fois de plus sur le fait qu'Haswell marquerait le point culminant de sa stratégie Ultrabook, grâce à un rendement énergétique très élevé, sans toutefois donner le moindre détail technique sur son architecture ni sur ses déclinaisons plus véloces.

Notez enfin que ce CPU prévu pour 2013 est déjà fonctionnel dans les labos du fondeur, desquels un exemplaire s'était échappé pour nous en apporter la preuve à l'IDF :

IDF: La grand-messe Intel ouvre ses portes

Comme chaque année, le mois de septembre est l'occasion de se rendre à l'Intel Developer Forum de San Francisco, évènement au cours duquel Intel fait le point sur ses plans autant à court terme qu'à long terme. De quoi en apprendre en peu plus, tout du moins nous l'espérons, sur les Sandy Bridge E et leur plateforme, sur Ivy Bridge et le 22 nanomètre, sur Cedar Trail et les tablettes ou encore sur l'architecture MIC et les successeurs de Larrabee.

La keynote d'ouverture de Paul Otellini, le CEO et Président d'Intel, est cependant restée inhabituellement sobre et vague en annonces, évitant notamment toute référence aux Sandy Bridge E dont la finalisation de la plateforme semblerait poser quelques problèmes de dernière minute.

Paul Otellini a principalement rappelé l'importance de proposer aux utilisateurs un environnement consistant dans lequel pourront circuler de manière transparente les informations entre les différents périphériques connectés qui sont en train de se multiplier à vive allure, ce qui inclut bien entendu la garantie d'une sécurisation suffisante. Le rachat de McAfee commencera d'ailleurs très bientôt à porter ses fruits à ce niveau avec l'arrivée de DeepSAFE tout d'abord réservée au monde professionnel et qui proposera, en combinaison avec les CPU de la marque, une sécurité renforcée contre les rootkits. Une première étape avant la généralisation de l'intégration plus poussée entre le CPU et le logiciel pour renforcer la sécurité sur toutes les plateformes proposées par le fondeur.

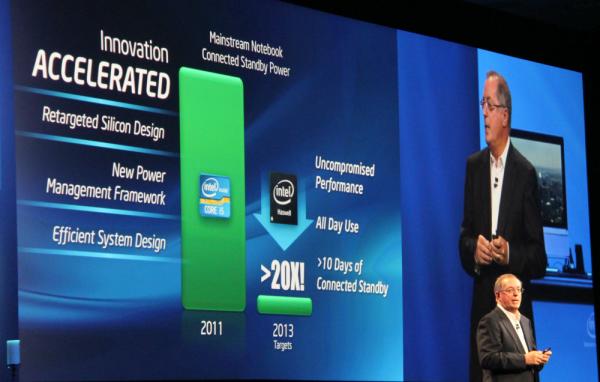

Pour faciliter une connectivité permanente, Paul Otellini indique se reposer sur le travail acharné entrepris par Intel depuis plusieurs années autour de la réduction de la consommation de la plateforme. En plus de faire baisser l'enveloppe thermique en charge de 50%, la plateforme Ultrabook de 2013, bâtie autour du CPU Haswell fabriqué en 22nm, devrait ainsi permettre une réduction de plus de 20X de la consommation en mode veille connectée, de quoi porter l'autonomie dans ce mode à plus de 10 jours ! Pour rappel, ce mode veille connectée permet par exemple d'avoir un accès instantané à ses emails lors du réveil du PC ainsi qu'à toutes autres données qui émergeront des nouveaux modèles d'utilisation ainsi rendus possibles (météo, news, état de remplissage du frigo ).

Paul Otellini et Andy Rubin, Senior Vice President of Mobile, Google.

Enfin, pour conclure ce premier keynote, Paul Otellini a annoncé un partenariat important, attendu depuis longtemps : la coopération renforcée avec Google afin d'optimiser la plateforme Android pour la famille Atom. Intel s'assure ainsi l'accès à un écosystème en pleine explosion et Google à une plateforme x86 qui est loin d'avoir dit ses derniers mots. Pour renforcer l'aspect concret de cette annonce, Paul Otellini a également brièvement montré un smartphone basé sur le SoC Atom Medfield et qui fera office de plateforme de développement pour Android 2.3.