Les derniers contenus liés aux tags SK Hynix et HMC

Les 2 contenus de cette page

GDDR5 8 Gbps et HBM 128 Go /s chez Hynix

Hybrid Memory Cube Gen2 en développement

GDDR5 8 Gbps et HBM 128 Go /s chez Hynix

Publié le 27/11/2014 à 09:41 par Marc Prieur

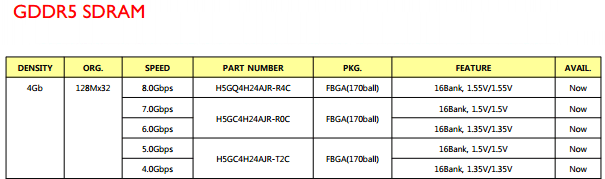

Dans son dernier catalogue destiné aux mémoires pour les puces graphiques, SK Hynix introduit une nouvelle GDDR5 à 8 Gbps soit 2000 MHz. La puce H5GQ4H24AJR-R4C est disponible en version 512 Mo et 32 bits, et offre seule une bande passante de 32 Go /s. Interfacée en 256 bits elle permet d'atteindre une bande passante de 256 Go /s contre 224 Go /s pour la GDDR5 7 Gbps qui prend place dans les GTX 970/980 par exemple.

Bien entendu une autre possibilité pour augmenter la bande passante mémoire disponible pour un GPU est d'augmenter la taille du bus, comme le fait AMD sur les R9 290/290X qui combinent de la mémoire à 5 Gbps et un bus 512 bits pour atteindre 320 Go /s.

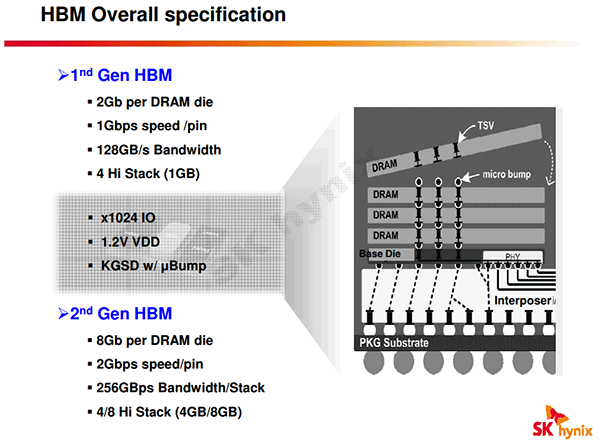

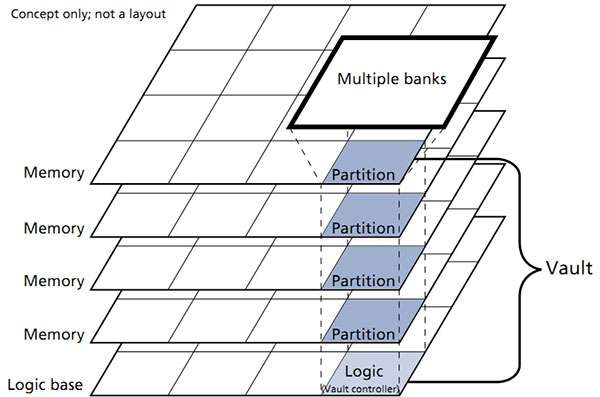

On note également la présence de mémoire HBM (High Bandwith Memory), avec cette fois une puce de... 128 Mo seulement (1 Gbits) ! A l'instar de la mémoire HMC (Hybrid Memory Cube), ce type de mémoire est composé d'un die logique de contrôleurs mémoire avec de multiples dies de mémoire, ici 4, le tout étant relié les uns aux autres par des TSV (Through Silicon Vias). Cette mémoire fonctionne a seulement 1 Gbps mais avec un bus 1024 bits, ce qui lui permet d'atteindre une bande passante pour une seule puce de 128 Go /s, 4 fois plus que la GDDR5 la plus rapide donc.

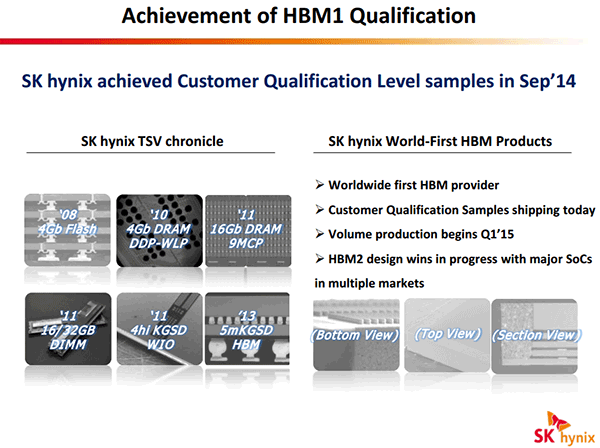

Si certains voient dans l'arrivée de la HBM au catalogue d'Hynix les prémices d'une association de la HBM avec des GPU AMD dès le 1er trimestre 2015, il faut temporiser ces ardeurs. Premièrement, la mémoire HBM n'est en fait pas nouvelle dans le catalogue Hynix, elle était déjà présente au troisième trimestre .

De plus, si AMD a effectivement collaboré avec SK Hynix au développement de la HBM, une puce de 128 Mo n'est pas assez dense pour être utilisée sur des GPU qui ont besoin de beaucoup plus de mémoire - il est plus qu'improbable d'avoir 16 à 32 puces HBM 1024 bits intégrées sur le packaging GPU ou sur le PCB ! Nvidia a déjà fait une présentation de sa génération de GPU Pascal prévue pour 2016 qui utilisera un type de mémoire proche, on pouvait voir 4 puces intégrées sur le packaging du GPU ce qui fait déjà un bus 4096-bit.

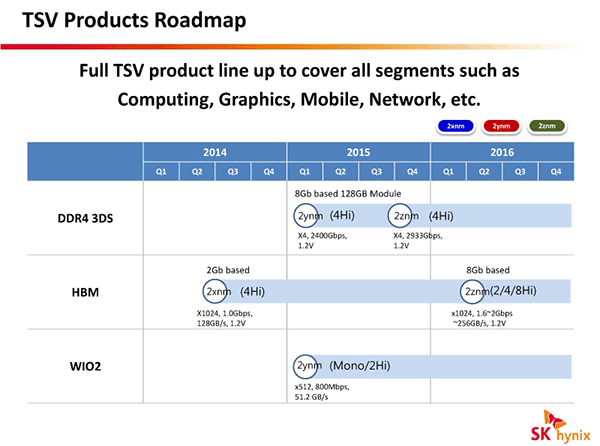

Toutefois la capacité annoncée pour cette puce HBM est en fait très étrange, SK Hynix a probablement fait une typo d'autant que la présence d'un "8G" dans la désignation fait penser à une capacité de 1 Go / 8 Gbits. C'est d'ailleurs de la HBM de 1 Go (4 die de 2 Gbits), atteignant également une bande passante de 128 Go /s avec un bus 1024 bits, qui a été qualifiée en septembre 2014 auprès des clients de SK Hynix, avec une production en volume devant débuter au cours du premier trimestre 2015 - on est donc loin de la disponibilité "Now" indiquée dans les catalogues des deux derniers trimestres. Courant 2016, une nouvelle génération de HBM doublera les débits alors que la capacité passera à 4 voir 8 Go (4 ou 8 die de 8 Gbits), mais on ne sait pas encore comment les fabricants de GPU utiliseront ces deux générations de HBM... est-ce qu'ils attendrons comme Nvidia le fait la seconde ou alors est-ce que AMD sautera le pas dès la première en 2015 ? L'avenir nous le dira !

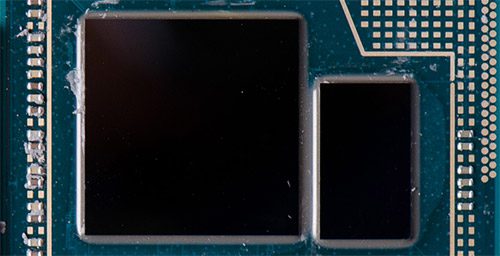

Reste que si la puce de 128 Mo HBM qui est au catalogue de SK Hynix existe, elle sera pour sa part plutôt utile sur des APU en tant que cache externe, comme le fait déjà Intel sur les Haswell GT3e / Iris Pro 5200 qui intègrent sur leur packaging une puce d'eDRAM maison de 128 Mo interfacée en 512 bits et offrant une bande passante de 50 Go /s dans chaque sens, ce qui permet un gain de performance net vu la faible bande passante de la mémoire centrale (25,6 Go /s en DDR3-1600 sur deux canaux).

Hybrid Memory Cube Gen2 en développement

Publié le 25/02/2014 à 19:05 par Guillaume Louel

L'Hybrid Memory Cube Consortium (fondé par Micron et Samsung en 2011, rejoint ensuite par Hynix et 120 sociétés donc ARM, IBM, Microsoft et Xilinx) vient de publier un communiqué indiquant le développement d'une seconde génération de cette mémoire. Pour rappel, le concept de l'HMC est de superposer plusieurs dies de mémoire DRAM par-dessus une die de logique, le tout étant relié par des TSV (Through Silicon Vias, des fils qui traversent les dies).

Nous avions parlé un peu plus en détail de la première version de cette spécification en septembre dernier, nous vous renvoyons vers cet article si vous souhaitez plus de détails.

La nouvelle spécification est encore au statut de « draft » (en préversion) et n'a été pour l'instant partagé qu'avec les membres du consortium dans le but d'être finalisé en mai 2014. La nouvelle version de la spec évoque des augmentations de bande passante, en doublant à 480 Go/s la bande passante totale des puces pour le modèle 4 liens, et 480 Go/s également pour le modèle huit liens (contre 320 dans la spec version 1.0).

Si Samsung et Hynix sont impliqués dans le développement du standard, Micron reste pour l'instant le seul constructeur à avoir produit des échantillons commerciaux.

Les 2 contenus de cette page