Infos sur l'AMD Bulldozer

Publié le 12/11/2009 à 10:32 par Marc Prieur

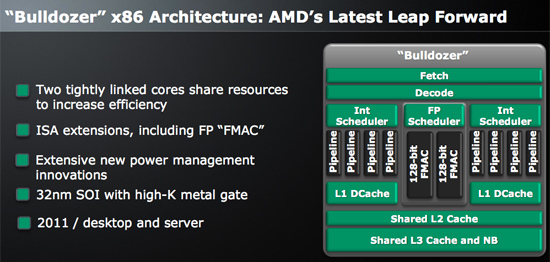

AMD a dévoilé au cours dune conférence destiné aux analystes des informations sur sa future architecture Bulldozer qui devrait arriver en 2011 et être gravée en 32nm. Première chose, chaque core physique sera vu en double par le système dexploitation, comme cest le cas chez Intel avec lHyperThreading. Mais cette fois, AMD va plus loin puisquil a bien dupliqué une partie de lexécution au sein de son Bulldozer.

Il existe ainsi au sein de chaque core Bulldozer deux blocs destinés à lexécution des entiers. Ces blocs sont complets, c'est-à-dire quils disposent chacun dun cache, dun scheduler et de 2 AGU + 2ALU. On notera au passage que sur un core K10, on trouve un seul bloc dexécution pour les entiers mais quil intègre 3 AGU et 3 ALU. En flottant un seul bloc dexécution sera présent. Il pourra être partagé entre les deux core logique et intégrera deux unités 128 bits de type FMAC, alors que le K10 intégrait 3 unités 128 bits mais spécialisés (FSTORE, FMUL et FADD).

Même si il ne sagit ici que des premières informations sur Bulldozer, on peut dire que cette architecture est innovante. Si il est impossible de savoir ce quelle vaudra par rapport au Sandy Bridge dIntel, il est certain quelle devrait offrir par rapport au K10 des avancées indéniables en terme de performances, particulièrement dans le domaine du calcul dentiers.

Vos réactions

Contenus relatifs

- [+] 09/05: AMD Ryzen 7 2700, Ryzen 5 2600 et I...

- [+] 04/05: Un Coffee Lake 8 coeurs en préparat...

- [+] 27/04: Le 10nm d'Intel (encore) retardé, l...

- [+] 26/04: Jim Keller rejoint... Intel !

- [+] 23/04: MAJ de notre test des Ryzen 7 2700X...

- [+] 20/04: MAJ de notre comparatif CPU géant

- [+] 19/04: AMD Ryzen 2700X et 2600X : Les même...

- [+] 19/04: 2008-2018 : tests de 62 processeurs...

- [+] 13/04: Les AMD Ryzen Pinnacle Ridge en pré...

- [+] 10/04: LGA4189 pour les Xeon Ice Lake !