Actualités divers

Kit 8 Go DDR3-3000 chez Corsair

Asetek s'attaque à Cooler Master

Shadow Rock 2 et Pure Wings 2 chez be quiet!

650 Watts en Fanless chez Enermax

Le Zalman FX100 Cube se montre

GTC: Performances GPU de Logan = GT 640M ?

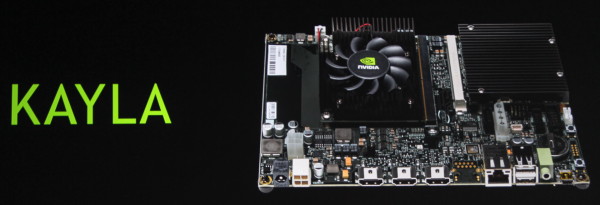

Durant la GTC 2013, nous avons pu nous entretenir avec Ian Buck qui est à l'origine de la première version de CUDA et actuellement General Manager chez Nvidia pour les technologies du GPU Computing. Interrogé au sujet de Kayla, la plateforme de développement CUDA on ARM équipée d'un GPU GK208, Ian Buck nous a indiqué que les performances GPU, au niveau de CUDA, étaient bel et bien représentatives de celles de Logan, sans vouloir en dire plus.

Bien que ce niveau de performances représente le bas de gamme sur PC, il s'agit d'une évolution énorme pour un SoC Tegra. Si le passage au 20nm et sans aucun doute plusieurs évolutions de l'architecture (avec probablement une réduction du nombre d'unités de texturing), faciliteront l'arrivée de l'architecture Kepler et de CUDA dans le monde ultra-mobile, il est difficile d'imaginer que ces 384 cores (ou équivalents) flexibles ne consommeront pas plus que les 72 cores avec pipeline fixe de Tegra 4.

De quoi nous laisser spéculer qu'avec Logan, Nvidia devra se contenter de versions bridées (en termes d'unités actives ou de fréquences) pour les "petites" tablettes et les superphones, mais compte par contre revoir ses prétentions à la hausse avec un SoC capable de monter en gamme pour viser les "grosses" tablettes voire des ultra-portables et bien entendu le successeur de Shield.

Parallèlement à cela, Ian Buck nous a indiqué que CUDA devrait progressivement devenir "power aware" et devenir capable de prendre en compte l'aspect consommation ou tout du moins de permettre aux développeurs de le faire. Cela se fera tout d'abord au niveau des outils tels que Nsight (et sa version Tegra) qui d'ici quelques temps reporteront des informations liées à la consommation.

Il est possible qu'à terme, les compilateurs CUDA, permettent optionnellement d'améliorer le rendement énergétique, mais cela est encore à l'état de recherche et prendra encore plusieurs années avant d'éventuellement se concrétiser. Globalement, la meilleure stratégie reste d'exécuter le plus rapidement une tâche pour retourner au repos dès que possible mais ce n'est pas toujours vrai, d'autant plus dans le cas d'une tâche continue telle que le rendu 3D sur GPU. Par exemple, calculer une valeur au lieu de la lire en mémoire peut avoir un léger impact sur les performances mais augmenter le rendement énergétique.

En plus de préparer le futur avec CUDA, dans l'immédiat, le plus important pour Nvidia est probablement d'arriver à convaincre un maximum de développeurs que faire l'effort nécessaire pour arriver à utiliser 2 threads ou plus à fréquence modérée offre un meilleur rendement que se contenter d'un seul thread mais des performances de la fréquence CPU maximale.

Correction du 01/07/2013: le nom du GPU que nous pensions être GK117 est en réalité GK208.

GTC: 5W Pour Tegra 4 et 1W pour Tegra 4i ?

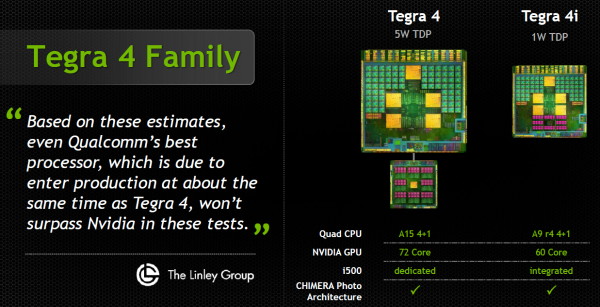

Lorsque nous avions rencontré Nvidia pour parler de l'architecture des Tegra 4 et 4i, il y a un point que le concepteur de ces SoC a catégoriquement refusé d'aborder : la consommation en charge et le TDP. Des chiffres délicats à avancer et à assumer puisque de toute évidence, la consommation maximale de Tegra 4 sera supérieure à celle de Tegra 3. Ceci n'étant bien entendu pas incompatible avec un rendement énergétique supérieur et avec une consommation en baisse lors de scénarios de types charge faible.

Lors d'une présentation dédiée aux investisseurs qui a suivi la keynote principale de la GTC, Jen-Hsun Huang, CEO de Nvidia, a avancé des chiffres concernant les TDP des futurs SoC : 5W pour Tegra 4 et 1W pour Tegra 4i. Deux chiffres relativement faibles, voire très faibles dans le cas du Tegra 4i qui intègre pour rappel 4 Cortex-A9 r4, un GPU relativement véloce et un modem 4G/LTE.

Pour comprendre ces chiffres, il faut cependant savoir que la définition du TDP est à géométrie variable, comme nous l'avions expliqué en nous intéressant de plus près au SDP d'Intel. Globalement le TDP représente la capacité de refroidissement nécessaire pour garantir le bon fonctionnement du composant. Historiquement cela représentait sa limite haute de consommation, mais progressivement, le fait de pouvoir fonctionner à une fréquence réduite pour éviter une surchauffe a été intégré à la définition même de "bon fonctionnement". Ajoutez-y les modes turbo et la prise en compte de l'inertie thermique et vous comprendrez qu'il devient difficile d'interpréter l'impact exact du TDP sur la consommation et sur les performances.

Les chiffres de 5W et de 1W avancés par Nvidia représentent ainsi probablement la capacité de dissipation nécessaire pour les variantes les moins gourmandes de Tegra 4 et de Tegra 4i. Des chiffres qui permettent de se faire une idée des types de designs et de formats qui pourront accueillir ces composants. De quoi confirmer que Tegra 4 est plutôt adapté à une tablette alors que Tegra 4i pourra être intégré facilement dans des smartphones compacts.

Difficile de dire par contre quel sera le niveau de performances soutenu autorisé par ces TDP puisqu'il est probable, comme c'est le cas pour la plupart des SoC actuels, que les Tegra 4 et 4i soient autorisés à consommer plus que cette valeur, jusqu'à atteindre une certaine température et voir leurs fréquences réduites. En plus de ces TDP, soit de la capacité de dissipation requise, il serait ainsi intéressant de connaître la capacité de dissipation conseillée par Nvidia pour pouvoir tirer le meilleur de ces SoC en termes de performances, notamment en ce qui concerne le jeu qui représente l'une des tâches les plus gourmandes qu'ils auront à exécuter.

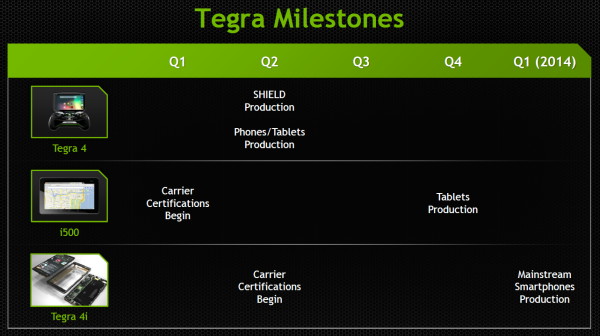

Enfin, notez que le CEO de Nvidia a précisé le timing de l'entrée en production des périphériques qui intégreront ces futurs SoC : Q2 2013 pour Shield, les tablettes et les superphones Tegra 4, Q4 2013 pour les tablettes Tegra 4 + modem i500 et enfin Q1 2014 pour les smartphones Tegra 4i (i500 intégré).

Des pertes pour Micron, malgré la hausse côté DRAM

Micron vient d'annoncer ses résultats pour le trimestre fiscal prenant fin le 28 février 2013. Le fabricant de mémoire atteint un chiffre d'affaires de 2,078 milliards de $, soit 3,4% de mieux qu'il y'a un an et surtout 13% de mieux qu'il y'a trois mois.

Le récent doublement des prix de la DRAM n'a pas encore vraiment touchée les contrats avec les OEM qui sont la principale source de revenus du constructeur et le résultat opérationnel reste négatif à 23 millions de $, en nette amélioration par rapport aux pertes de 204 millions et 97 millions enregistrées un an et trois mois auparavant. La perte nette ne faiblit par contre pas à 286 millions de $ du fait d'écritures comptables liées au rachat d'Elpida et Rexchip (120 millions) et à la revente d'une usine de wafer de 200m à Avezzano en Italie.

La marge brute est en hausse avec 18%, contre 12% au trimestre précédent, Micron attribuant ce gain à une baisse du coût de fabrication. Sur la période les ventes de DRAM sont en hausse de 24%, avec une hausse de volume de bits de 38% contrecarrée par une baisse du prix de vente moyen de 10%.

Ceci s'explique par le retrait annoncé début janvier de Nanya de la joint-venture Inotera qu'il avait avec Micron et qui fait que Micron achète désormais 95% du fabricant de mémoire Taiwanais, d'où la hausse du volume importante et la baisse du prix moyen malgré la tendance du marché, les produits Inotera étant moins haut de gamme et chers que ceux de Micron.

Côté NAND Flash la hausse est de 8%, avec une hausse du volume de 13% mais une baisse du prix moyen. Les ventes de SSD sont en hausse de 40% sur un trimestre.

Pour le prochain trimestre Micron estime que le prix de vente et le coût de production moyen de sa NAND sera en baisse de 5% environ, associé à une hausse du volume produit de 5 à 9%. Côté DRAM Micron s'attend à une hausse de son prix de vente moyen de 5% pour une baisse du prix de production de 5 à 9% et une hausse du volume de 2%.

Par rapport aux prix du marché au jour le jour de la mémoire la hausse est très faible, ceci s'expliquant encore une fois par le fait qu'une grosse partie des volumes se font sur la base de contrats d'approvisionnement dont les prix sont fixés à l'avance et dont les prix ne varient pas aussi vite.

Micron indique de plus qu'il va augmenter la part de wafer DRAM en provenance de Inotera dans sa production globale de DRAM, le mix produit sera donc différent et moins haut de gamme, et qu'il va reconfigurer une partie de ses propres lignes dédiées à la fabrication de DRAM en lignes de fabrication Flash NAND afin de ne pas être en surcapacité côté DRAM, d'autant que lorsque le rachat d'Elpida sera terminé cela augmentera de 45% ses capacités côté DRAM.

Prix de la DDR3 : enfin une accalmie

Les prix de la mémoire semblent enfin se calmer, après avoir encore augmenté en flèche jusqu'à la mi-mars. Au plus haut, il fallait en effet compter 3,478$ pour une puce de 512 Mo de DDR3-1600, contre 2,01$ fin novembre (+73%) et 1,748$ pour une puce de 256 Mo contre 0,82$ fin novembre (+113%).

Pour faire une barrette de 4 Go DDR3-1600 la moins chère possible il fallait utiliser en fin d'année passée des puces 256 Mo pour un coût total en DDR3 de 13,12$, contre des puces 512 Mo pour 27,824$ (+112%) mi-mars.

Depuis un peu moins d'une semaine la hausse est terminée et on observe même un léger repli : il faut en effet compter 1,68$ pour 256 Mo de DDR3-1600 et 3,403$ pour 512 Mo. Les prix ont tout de même plus que doublé pour une barrette de 4 Go en l'espace de 4 mois, une hausse qui n'a pas encore été complètement répercutée sur les prix de vente en France grâce aux stocks des divers intervenants. Reste à savoir quelle sera l'évolution des prix dans les prochaines semaines

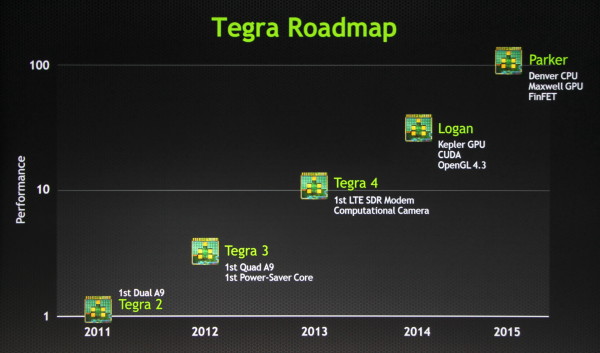

GTC: Le futur de Tegra: CUDA, Logan, Parker

Après la roadmap GeForce, Nvidia nous en a dit un peu plus sur la roadmap des SoC Tegra. Si certains ont été quelque peu déçus de ne pas retrouver un GPU plus moderne dans Tegra 4, cela est en passe de changer. Jen-Hsun Huang a ainsi confirmé que la prochaine architecture Tegra, Logan, intégrerait enfin une évolution GPU majeure qui fera le pont avec les technologies qui nous retrouvons dans la gamme GeForce traditionnelles.

Ainsi, le GPU de Logan sera dérivé de l'architecture Kepler avec un support complet d'OpenGL 4.3 et surtout de CUDA 5 pour permettre d'exploiter la puissance de calcul du GPU d'une manière plus flexible, par exemple pour le traitement d'images. En plus de sa plateforme propriétaire CUDA, nul doute que Nvidia supportera également la plateforme ouverte OpenCL, qui, dernièrement, a enfin reçu un support clair de la part de Google en ce qui concerne Android.

Pour le reste, il est probable que Logan reprenne les mêmes cores Cortex-A15 que Tegra 4 et soit fabriqué en 20 nanomètres. Jen-Hsun Huang a précisé que si Tegra 4 est arrivé en retard, Tegra 4i est de son côté arrivé légèrement en avance alors que Logan devrait être à l'heure avec des premiers prototypes à la fin de l'année et une production qui débutera début 2014. Vous pouvez donc vous attendre à une annonce de Tegra 5 au CES 2014.

Tout ceci n'est cependant qu'une confirmation de ce que nous supposions déjà. La nouveauté est l'arrivée de quelques premières informations sur le successeur de Logan : Parker. Ce dernier arrivera en 2015 et intègrera les premiers cores ARM conçus en interne par Nvidia et basés sur l'architecture ARMv8 qui supporte le 64-bit, nom de code Denver. Au niveau du GPU, Parker passera à la génération Maxwell, avec seulement une année de décalage par rapport aux gros GPU dekstop, les architectures GPU étant dorénavant unifiées entre les différentes divisions de Nvidia.

Parker devrait également être la première puce conçue par Nvidia en vue de l'utilisation d'un procédé de fabrication de type FinFET ("transistors 3D) et nous pouvons supposer qu'il s'agira alors du 14nm.