Les derniers contenus liés aux tags Samsung et HMC

Hybrid Memory Cube Gen2 en développement

Un consortium pour l'Hybrid Memory Cube

Hybrid Memory Cube Gen2 en développement

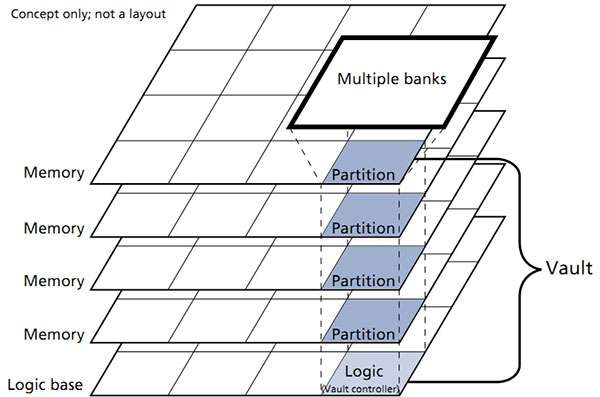

L'Hybrid Memory Cube Consortium (fondé par Micron et Samsung en 2011, rejoint ensuite par Hynix et 120 sociétés donc ARM, IBM, Microsoft et Xilinx) vient de publier un communiqué indiquant le développement d'une seconde génération de cette mémoire. Pour rappel, le concept de l'HMC est de superposer plusieurs dies de mémoire DRAM par-dessus une die de logique, le tout étant relié par des TSV (Through Silicon Vias, des fils qui traversent les dies).

Nous avions parlé un peu plus en détail de la première version de cette spécification en septembre dernier, nous vous renvoyons vers cet article si vous souhaitez plus de détails.

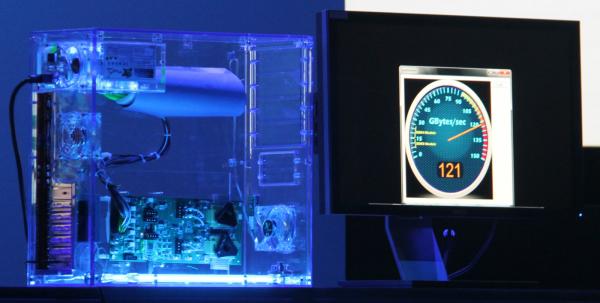

La nouvelle spécification est encore au statut de « draft » (en préversion) et n'a été pour l'instant partagé qu'avec les membres du consortium dans le but d'être finalisé en mai 2014. La nouvelle version de la spec évoque des augmentations de bande passante, en doublant à 480 Go/s la bande passante totale des puces pour le modèle 4 liens, et 480 Go/s également pour le modèle huit liens (contre 320 dans la spec version 1.0).

Si Samsung et Hynix sont impliqués dans le développement du standard, Micron reste pour l'instant le seul constructeur à avoir produit des échantillons commerciaux.

Un consortium pour l'Hybrid Memory Cube

Démontrée par Intel et Micron lors de l'IDF, la technologie Hybrid Memory Cube s'ettoffe un peu aujourd'hui avec l'arrivée de Samsung. Micron et Samsung ont en effet annoncé la création d'un consortium dédié à cette technologie dans le but de développer une spécification commune pour l'industrie. Une préversion de la spécification devrait être partagée sous peu par le consortium afin de recueillir suggestions et remarques. La version finale est annoncée pour 2012.

Pour rappel, l'Hybrid Memory Cube consiste à superposer plusieurs die de mémoire DRAM avec un die logique (le processeur). Le prototype présenté lors de l'IDF disposait d'une bande passante de 128 Go/s obtenus avec quatre die DRAM qui communiquent directement avec la couche logique par le biais d'interconnexions qui traversent les die (through-silicon vias).