| |

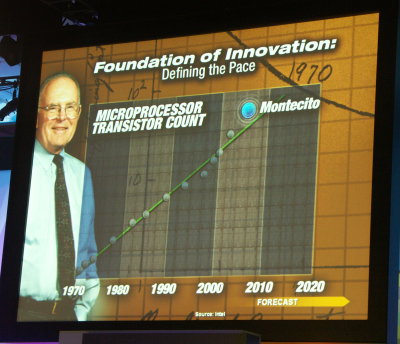

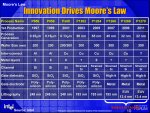

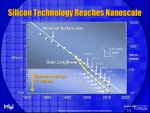

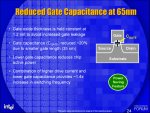

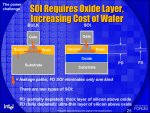

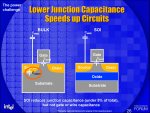

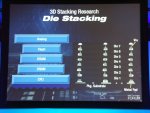

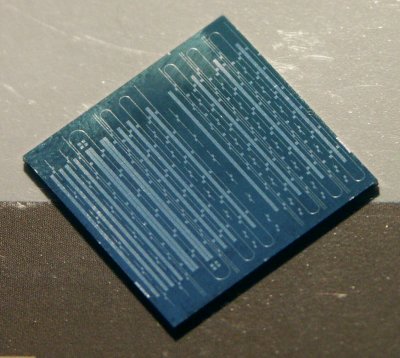

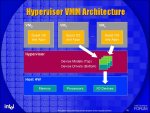

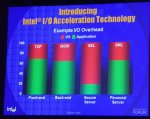

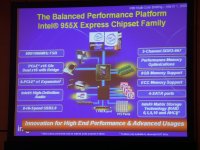

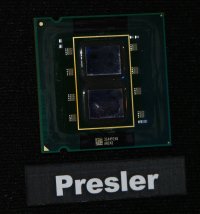

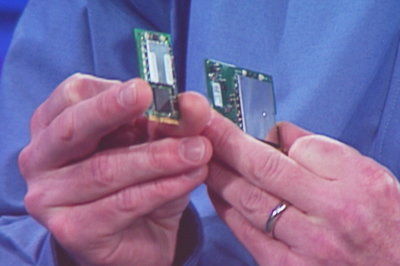

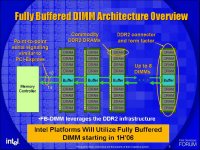

| IDF - Printemps 2005 Divers Publié le Mercredi 9 Mars 2005 par Damien Triolet URL: /articles/556-1/idf-printemps-2005.html Page 1 - Introduction  LIntel Developer Forum, ou la grande messe semestrielle dIntel, sest tenu la semaine passée au Moscone Center de San Francisco. Loccasion pour Intel de réaffirmer publiquement ses choix technologiques mais également de former lindustrie aux technologies récentes et futures afin de sassurer de leur pérennité. Cet IDF avait une saveur particulière et ce pour plusieurs raisons. La première concerne la stratégie multi-core dIntel, dont nous vous avons dévoilé les grandes lignes lors de notre reportage sur lIDF de septembre 2004, qui se voit concrétisée. La seconde concerne le long terme, Intel ayant décidé de rassurer sur les possibilités futures dévolution du micro-processeur. Celui-ci a encore un long chemin devant lui ! Et la dernière est plus complexe et subtile. Intel a entrepris une réorganisation interne importante et comme une grande partie de lindustrie et de la presse, nous observons cette évolution avec grand intérêt.  Autre particularité de cet IDF, il marque les 40 ans de la fameuse "loi" de Moore dont nous entendons parler depuis longtemps sous diverses formes daprès les besoins marketing du moment. Aujourdhui elle revient en force dans sa version "le nombre de transistors double tous les 18 mois" avec laugmentation massive du nombre de transistors accélérée par le passage au multi-core et grâce à certains CPU professionnels équipés dun cache énorme (comme le Montecito avec ses 26 Mo de cache). 40 ans oblige, la loi de Moore était évoquée à tour de bras durant cet IDF, pas une présentation ny échappait. Il convient bien entendu de relativiser son importance tant elle est facile à démonter. Les CPU multi-cores devraient dailleurs sonner le glas de cette "loi" en voyant leur nombre de transistors évoluer beaucoup plus rapidement. Cest dailleurs déjà le cas puisque daprès la loi de Moore le Montecito a 5 ans davance ! Page 2 - R&D : CMOS  Lors de cet IDF, Intel a mis un point dhonneur à rassurer sur les possibilités technologiques futures. Il a souvent été question de limitations à moyen terme de la technologie CMOS, au niveau des performances des transistors et de leur fabrication mais Intel affirme ici clairement quil y a encore de la marge et lexprime principalement via 3 technologies sur lesquelles leur département R&D travaille. Lors de cet IDF, Intel a mis un point dhonneur à rassurer sur les possibilités technologiques futures. Il a souvent été question de limitations à moyen terme de la technologie CMOS, au niveau des performances des transistors et de leur fabrication mais Intel affirme ici clairement quil y a encore de la marge et lexprime principalement via 3 technologies sur lesquelles leur département R&D travaille.Evolution des process de fabricationIl sagit là du moyen le plus simple de faire évoluer les transistors, étant donné que faire évoluer le process permet de disposer de transistors plus performants (fréquence accrue) et plus petits (il devient alors possible den placer plus sur un CPU à coût identique). Le succès dIntel est dû en grande partie à ses process de fabrication et à ses nombreuses usines qui lui permettent de fabriquer des processeurs avec un volume et un yield qui font rêver beaucoup dacteurs de cette industrie.    Fin de cette année ou début 2006, Intel devrait commercialiser les premiers processeurs fabriqués en 65 nm. Ce process utilisera globalement les mêmes technologies que le 90 nm actuel. Il reprendra donc le Strained Silicon qui permet daugmenter la vitesse de déplacement des électrons dans le transistor et donc de faciliter la montée en fréquence et/ou de réduire la consommation. En 65 nm le Strained Silicon en sera à sa seconde génération et permet selon Intel daugmenter de 30% les performances des transistors.    Tout en faisant lapologie de cette technologie, Intel nhésite pas à démonter celle de son concurrent, le SOI. Il permet de réduire les courants de fuite (et donc qui ne servent à rien dautre quà faire chauffer le processeur) et donc la consommation du processeur. AMD semble en être très satisfait, et la faible dissipation thermique des Athlon 64 va dans ce sens, mais selon Intel le SOI tel quutilisé par AMD ("partially depleted") na aucun intérêt puisquil ne réduit quun des nombreux types de courant de fuite, augmente significativement le coût de fabrication et voit son utilité réduite avec lévolution des process. Intel nenvisagera le SOI quen version "fully depleted", cest-à-dire avec une couche extra-fine, mais ce nest pas pour tout de suite et la décision sera prise sur base de la balance coûts/gains de cette solution dans quelques années.    En 2007, avec le process 45 nm, devrait arriver un changement important avec lutilisation dun isolant de grille de type High K et délectrodes métalliques en lieu et place de loxyde de silicium et du poly-silicon utilisés actuellement. Ce changement important réduira la capacitance de la grille (ce qui permet daugmenter la vitesse des transistors) et réduira les courants de fuite dun facteur supérieur à 100, réduisant ainsi drastiquement la consommation. De quoi fabriquer des processeurs quadri-cores à haute fréquence et qui ne consommeront pas plus de 100 Watts ?   Die StackingIl ne sagit pas réellement dune nouvelle technologie étant donné quelle est utilisée depuis longtemps dans les mémoires. Le Die Stacking consiste à empiler les dies les uns sur les autres et à les connecter entre eux et/ou directement sur le socket. Il y a bien entendu des limitations physiques, tant au niveau de la réalisation de ces connexions mais également au niveau de la dissipation thermique. Empiler 4 Prescott pourrait en effet être dangereux. Empiler des cores qui chauffent moins est envisageable, mais dans "limmédiat" il est plutôt question de dies totalement différents : par exemple un CPU, un northbridge, un contrôleur réseau et de la RAM très rapides empilés. Le gain en place serait conséquent et les coûts réduits. Si lon a du mal à envisager ce genre de chose avec les CPU desktop actuels, il en est tout autrement avec les Pentium M LV et ULV avec lesquels cette technologie prendrait tout son sens.    Reste bien entendu à mettre au point des systèmes de packaging efficaces et fiables (par exemple pour éviter décraser les dies lors du montage dun système de refroidissement), la connectique et de résoudre la problème du dégagement thermique. Intel indique pour ce dernier point que de nombreuses solutions existent et quil ne remettra pas en cause le Die Stacking. Le CPU photoniqueUn problème de plus en plus important dans les CPU est le délai de propagation du signal dans les interconnexions. Il y a quelques générations il était considéré comme négligeable mais aujourdhui ce nest plus le cas. La vitesse des transistors a augmenté dans des proportions très importantes alors que le délai de propagation est resté plus ou moins constant ce qui est logique étant donné que avec la miniaturisation, bien quil ait une distance plus réduite à parcourir, le signal passe par des interconnexions plus fines qui ont donc une résistance plus élevée réduisant ainsi la vitesse du signal. Lun dans lautre le délai de propagation ne se réduit pas.  Ce die distribué par Intel contient pas moins de 8 lasers Si un signal doit se déplacer dun bloc à un autre du CPU, il ne peut plus le faire en un cycle. Il faut placer des répétiteurs qui augmentent la consommation et la latence du signal. Il y a bien entendu des solutions via lamélioration du process de fabrication, mais ça ne devrait pas être suffisant à long terme.    La solution pourrait bien être lutilisation de la photonique sur silicium qui revient à utiliser des photons (lumière) au lieu délectrons pour la transmission des signaux. Les gains sont énormes puisque le signal peut se déplacer plus rapidement et se dégrader beaucoup moins. On pourrait ainsi imaginer à terme une connexion photonique vers le cache L2 voir même des connexions photoniques externes au CPU pour connecter 2 die entre eux et un tas dautres utilisations dans des domaines très variés.    Il sagit cependant dun défi difficile à réaliser étant donné quidéalement les éléments photoniques devraient être fabriquées de la même manière que les transistors. Mais manque de chance, la photonique a besoin dune source émettrice de lumière : le laser. Or, ce lui-ci, pour fonctionner doit disposer dun matériau qui émet facilement et en masse des photons, ce qui nest absolument pas le cas du silicium.    Sans issue ? Pas pour Intel qui annonce avoir fabriqué le premier laser continu sur silicium grâce à leffet Raman, effet quantique qui permet notamment damplifier les signaux optiques. Une pompe amène un flux de photons et lamplificateur Raman se charge damplifier le signal dune manière très efficace, leffet Raman étant 10.000 fois plus fort dans le silicium que dans le fibre optique. Ca fonctionne alors ? Pas encore car un autre problème subsiste et empêche le laser dêtre réellement utilisable. En temps normal, le silicium est transparent pour la lumière infrarouge mais pendant lamplification le nombre de photons augmente suffisamment pour que 2 dentre eux heurtent régulièrement un atome de silicium en même temps, dégageant un électron qui va alors absorber de nombreux photons et ainsi réduire a néant leffet Raman. Intel indique cependant quil sagit dun premier pas et que les différents problèmes qui subsistent devraient être résolus dans les années à venir. Le CMOS est toujours bien vivantAvec les futurs process de fabrication CMOS, le Die Stacking et la photonique sur silicium Intel a de quoi voir venir. Il y a là en effet tout ce qui est nécessaire pour continuer à fabriquer des CPU toujours plus évolués et performants pendant au moins 2 décennies ! Intel nhésite dailleurs pas à brosser un rapide portrait du CPU de 2015 : il sera fortement optimisé pour le multi-threading, intégrera plusieurs cores et de plus en plus dunités spécialisées un peu comme commencera à le faire IBM lannée prochaine avec le Cell.    Page 3 - Intel 3.0 Intel 3.0Jusquil y a peu, le développement des produits Intel était scindé en 2 divisions principales : lArchitecture Group qui soccupait de tout ce qui était processeur classique et chipset et le Communication Group qui avait à sa charge les mémoire flash, les processeurs pour périphériques handheld (PDA, GSM ) et les produits réseaux. Aujourdhui les produits Intel ont été répartis en 5 groupes : le Mobility Group (plateformes portable et handheld), le Digital Enterprise Group (plateforme professionnelle), le Digital Home Group (plateforme grand public), le Digital Health Group (tout ce qui touche à la santé, la recherche médicale etc.) et le Channel Products Group (soccupe de la localisation et de ladaptation des produits Intel sur des marchés spécifiques).  Certains analystes qualifient ce changement de passage à la version 3.0 dIntel. Intel a dabord été un fabriquant de mémoires, puis un fabriquant de processeurs et maintenant peut être défini comme un fabriquant de plateformes. Chaque division est relativement indépendante, tant au niveau technologique que marketing, ce qui pourrait amener des contradictions entre elles. La stratégie marketing dIntel pourrait également changer et devenir plus agressive et spécifique, le marché se voir cadenassé et laspect technologique passer au second plan. Mais ces changements pourraient également être très bénéfiques pour lutilisateur final avec des produits qui correspondront mieux à leurs besoins et qui sadapteront plus rapidement aux évolutions de ces besoins. 2005 et 2006 permettront de juger les bienfaits de cette réorganisation. Certains analystes qualifient ce changement de passage à la version 3.0 dIntel. Intel a dabord été un fabriquant de mémoires, puis un fabriquant de processeurs et maintenant peut être défini comme un fabriquant de plateformes. Chaque division est relativement indépendante, tant au niveau technologique que marketing, ce qui pourrait amener des contradictions entre elles. La stratégie marketing dIntel pourrait également changer et devenir plus agressive et spécifique, le marché se voir cadenassé et laspect technologique passer au second plan. Mais ces changements pourraient également être très bénéfiques pour lutilisateur final avec des produits qui correspondront mieux à leurs besoins et qui sadapteront plus rapidement aux évolutions de ces besoins. 2005 et 2006 permettront de juger les bienfaits de cette réorganisation. A côté de cette réorganisation, Intel va également changer de CEO. Craig Barrett a décidé de céder sa place à Paul Otellini qui deviendra courant mai le 5ème CEO dIntel, après Robert Noyce, Gordon Moore, Andy Grove et Craig Barrett. Contrairement à ses prédécesseurs qui avaient tous un passé dingénieur brillant, Paul Otellini, actuellement President et COO, est issu du marketing et des ventes. De gros changements en perspective ? Pas du tout selon lintéressé qui insiste sur le fait que à côté de ce quil apportera de nouveau trôneront toujours les 20 années dhistoire dIntel. Ce changement de CEO entraîne bien entendu des changements de postes en cascade. En amont, Craig Barrett va remplacer Andy Grove au poste de Chairman A côté de cette réorganisation, Intel va également changer de CEO. Craig Barrett a décidé de céder sa place à Paul Otellini qui deviendra courant mai le 5ème CEO dIntel, après Robert Noyce, Gordon Moore, Andy Grove et Craig Barrett. Contrairement à ses prédécesseurs qui avaient tous un passé dingénieur brillant, Paul Otellini, actuellement President et COO, est issu du marketing et des ventes. De gros changements en perspective ? Pas du tout selon lintéressé qui insiste sur le fait que à côté de ce quil apportera de nouveau trôneront toujours les 20 années dhistoire dIntel. Ce changement de CEO entraîne bien entendu des changements de postes en cascade. En amont, Craig Barrett va remplacer Andy Grove au poste de Chairman  mais en aval rien na encore été communiqué. Qui va prendre la place de President et de COO ? Pourquoi pas le très charismatique Pat Gelsinger ? La réorganisation ayant supprimé le poste de Chief Technology Officer quil occupait, il est passé General Manager du Digital Enterprise Group et a donc vu son champ daction réduit. mais en aval rien na encore été communiqué. Qui va prendre la place de President et de COO ? Pourquoi pas le très charismatique Pat Gelsinger ? La réorganisation ayant supprimé le poste de Chief Technology Officer quil occupait, il est passé General Manager du Digital Enterprise Group et a donc vu son champ daction réduit.Vous laurez compris, Intel est en pleine mutation et ceci à un moment technologique crucial : labandon de la vitesse du processeur au profit des possibilités de la plateforme. Un virage à 180 degrés difficile à réaliser, mais Intel compte bien le réussir et a décidé de lamorcer dès aujourdhui ! Page 4 - Technologies VTVT ou Virtualization Technology (nom de code Vanderpool/Silvervale) permettra de démocratiser les systèmes de virtualisation du hardware, cest-à-dire qui permettent de faire tourner plusieurs systèmes dexploitation sur une même machine. Actuellement des logiciels comme VMware permettent de le faire mais avec certaines contraintes et sont réservés au monde professionnel. VT simplifiera le tout. Une des utilités pour le grand public pourra par exemple être davoir un OS dédié à la sécurité de la machine. Si lOS principal est infecté par un virus (du genre coriace, qui empêche lantivirus de se mettre à jour et/ou de fonctionner par exemple), lOS "gardien" sera capable de le nettoyer et de le déconnecter du réseau temporairement pour éviter la propagation du virus. Bien entendu nous pouvons malheureusement compter sur les aimables développeurs de virus et autres spywares pour mettre au point des versions spéciales VT ou tout du moins essayer. Pour être complètement fonctionnel VT demandera un support des OS, de certains drivers et des cartes graphiques. Une fois tout cela en place, VT pourra marquer un tournant majeur dans larchitecture de nos PC.    IAMTIAMT est destiné à aider les administrateurs de parc informatique à gérer celui-ci plus facilement, plus rapidement et à moindre coût, le but étant de sortir le moins souvent de son bureau pour régler tout problème qui pourrait survenir. I/OATI/OAT est une nouveauté dévoilée pour la première fois lors de cet IDF. Avec laugmentation des débits réseau, la charge CPU utilisée pour le gérer est devenue significative. Intel a donc décidé dadapter la plateforme de manière à optimiser le traitement des données qui circulent sur le réseau.    LTLT ou LaGrande Technology est destinée à permettre au système dexploitation daugmenter la sécurité de lordinateur ce qui devrait être le cas avec Longhorn et Palladium. Malheureusement, certains détails sont encore très flous à son sujet et la technologie de Palladium de Microsoft a déjà fait couler beaucoup dencre au sujet de ses dérives possibles. Personne nest contre une augmentation de la sécurité, mais personne ne voudrait voir les majors de la musique conquérir son ordinateur LT / Palladium devraient envahir nos PC courant 2006 et avoir des implications au niveau du CPU, du chipset, de la carte graphique etc Les contenus protégés devraient ainsi être cryptés dans tous les éléments du PC. Les abus possibles sont aussi nombreux que les nouveaux business très rentables qui en découleront. EM64T  Et bien entendu lEM64T, réponse au x86-64 dAMD, est maintenant mis en avant par Intel bien que le fondeur relativise systématiquement son importance. LEM64T permet principalement de mieux optimiser le code et de pouvoir adresser plus de 4 Go de mémoire. Bien entendu le chipset entre lui aussi dans le support de la mémoire : les futurs chipsets i945 et i955X seront ainsi limités à 8 Go. Microsoft était présent à lIDF pour rappeler aux développeurs quils devaient passer au 64 bits le plus rapidement possible. Windows Serveur 2003 64 bits sera disponible dans 1 mois et Windows XP 64 bits dans 2 mois. Seule petit ombre au tableau du 64 bits, Intel a fait limpasse sur cette technologie pour ses CPU mobiles. Et bien entendu lEM64T, réponse au x86-64 dAMD, est maintenant mis en avant par Intel bien que le fondeur relativise systématiquement son importance. LEM64T permet principalement de mieux optimiser le code et de pouvoir adresser plus de 4 Go de mémoire. Bien entendu le chipset entre lui aussi dans le support de la mémoire : les futurs chipsets i945 et i955X seront ainsi limités à 8 Go. Microsoft était présent à lIDF pour rappeler aux développeurs quils devaient passer au 64 bits le plus rapidement possible. Windows Serveur 2003 64 bits sera disponible dans 1 mois et Windows XP 64 bits dans 2 mois. Seule petit ombre au tableau du 64 bits, Intel a fait limpasse sur cette technologie pour ses CPU mobiles.Page 5 - Desktop Desktop  Anchor Creek sera la plateforme haut de gamme de 2005 et mainstream de 2006 pour le marché Home alors que Lyndon sera la version Office. Ces plateformes supporteront les Pentium Dual-Core de type Smithfield et Presler mais également leurs équivalents Single-Core (Pentium 4 et Cedarmill). Ce nest que après la mi-2006 que la plateforme Averill devrait débarquer avec à son bord de nouvelles technologies : VT, IAMT, I/OAT et LT.  Le chipset i955X de la plateforme Anchor Creek apportera quelques nouveautés comme le support de la DDR2-667 et de 2 ports PCI Express "graphiques" semblables à la solution SLI de NVIDIA. Mais sera-t-il possible de faire tourner du SLI sur une carte-mère Intel ? Probablement pas si NVIDIA ne revoit pas sa politique de drivers. ATI pourrait cependant être très intéressé par la solution dIntel... Le chipset i955X de la plateforme Anchor Creek apportera quelques nouveautés comme le support de la DDR2-667 et de 2 ports PCI Express "graphiques" semblables à la solution SLI de NVIDIA. Mais sera-t-il possible de faire tourner du SLI sur une carte-mère Intel ? Probablement pas si NVIDIA ne revoit pas sa politique de drivers. ATI pourrait cependant être très intéressé par la solution dIntel...Dual-core desktopLongtemps attendu, le Pentium 5 ne verra finalement pas le jour. Intel a décidé de se séparer du numéro et de ne conserver que la marque Pentium, un choix stratégique qui sépare le nom du produit de la technologie. Les processeurs dual-cores pour PC de bureau se nommeront ainsi Pentium eXtreme Edition pour le très haut de gamme et Pentium D pour le marché haut de gamme dans un premier temps et pour le marché mainstream par la suite. Ils devraient être disponibles avant lété. Le processeur, nom de code Smithfield, est fabriqué en un seul bloc sur le process 90 nm actuel mais bien quil nutilise "que" la version 1 Mo du core Prescott, il intègre les optimisations liées à la consommation du core Prescott 2 Mo. Malgré cela son enveloppe thermique reste énorme puisque de 130W à 3.2 GHz. Intel a dailleurs dû faire évoluer son système de refroidissement pour prendre en compte ce dégagement thermique, mais celui-ci reste dune taille classique et ne semble pas excessivement bruyant.   Page 6 - Mobile Mobile  Intel a modifié la roadmap de ses plateformes mobiles. Le retard de Sonoma, annoncé fin janvier, se répercute sur Napa qui passe de fin 2005 à début 2006. Le nouveau chipset, en plus de supporter le Dual-Core, intégrera un nouveau core graphique et un nouveau composant WiFi, Golan qui sera plus petit et consommera beaucoup moins que le composant actuel qui est relativement gourmand.  Golan sera un composant WiFi plus compact et nettement plus économe Dual-core mobileAttendu pour fin 2005, le Yonah sera le premier CPU dual-core destiné aux portables. Comme le Smithfield, le Yonah utilisera un seul die intégrant les 2 cores. Par contre les similitudes sarrêtent là. Le Yonah sera fabriqué sur le nouveau process, le 65 nm. Une obligation étant donné que dans un portable on ne peut pas se permettre de placer une source de chaleur démesurée. Mooly Eden, Vice-President du Mobility Group annonce dailleurs avec une certaine fierté que la consommation moyenne du Yonah ne dépassera pas celle des derniers Pentium M, malgré la présence de 2 cores et ce grâce à des systèmes déconomie dénergie plus avancés avec notamment la possibilité de désactiver lun des 2 cores.  Particularité du Yonah, cest le seul CPU Dual-Core de la roadmap dIntel à utiliser un cache L2 partagé au lieu de 2 caches distincts. Celui-ci sera de 2 Mo et devrait conserver les performances du cache L2 du Dothan. Cest également le seul CPU de la roadmap dIntel à ne pas supporter lEMT64 ! Le 64 bits mobile ne devrait donc pas être disponible avant fin 2006 chez Intel, ce qui pourrait faire laffaire dAMD et de ses Turion, bien que lutilité du 64 bits jusque là est encore à démontrer. Le Yonah intégrera quelques optimisations au niveau de son architecture. Intel a notamment voulu augmenter ses performances en FPU et SSE de manière à les uniformiser sur sa gamme de CPU. Les Pentium M actuels sont en effet un petit peu en retrait à ce niveau par rapport aux Pentium 4. Pour y parvenir, Intel a décidé daugmenter le débit des decoders en instructions SSE. Les 3 decoders ont maintenant la capacité de traiter les instructions SSE. Ensuite certaines opérations SSE pourront également être fusionnées par le Micro Ops Fusion Engine comme cest déjà le cas pour les autres instructions dans le Pentium M actuel. Et enfin le SSE3 sera supporté et la FPU sera légèrement retouchée pour améliorer ses performances... dans les jeux. Le fait que Mooly Eden fasse mention à lutilisation ludique du Pentium M est lourd de sens. Le Yonah naurait-il pas sa place autre part que dans un portable ? Page 7 - Serveur/Workstation Serveur/Workstation  La plateforme Itanium conserve le même et vieillissant chipset 8870 pour 2005 et 2006, Intel ayant abandonné le développement de Bayshore, un nouveau chipset supportant les dernières technologies comme le PCI Express.   Nous avons ajouté aux plateformes Xeon, une plateforme équipée dun Pentium D qui utilisera le Mukilteo, un chipset serveur/workstation uni-processeur. Il sera une alternative intéressante niveau coût aux solutions bi-processeurs de 2005. Il faudra attendre 2006 pour voir débarquer les Xeon Dual-Core et une plateforme qui apportera son lot de nouveautés : VT, IAMT et I/OAT.  Dans les années à venir, les plateformes serveur dIntel devraient disposer dune nouvelle interface mémoire qui fera appel à la FB-DIMM (fully-buffered DIMMM) qui consiste à placer un intermédiaire entre les puces mémoire et le contrôleur. Cela permet de conserver des puces mémoires classiques avec un contrôleur très différent, lintermédiaire faisant en quelque sorte la conversion. Avec le FB-DIMM le connexion entre lintermédiaire et le contrôleur sera de type série, semblable au PCI Express, elle offrira des débits supérieurs et surtout permettra dutiliser plus de barrettes mémoire sur une même machine. Dans les années à venir, les plateformes serveur dIntel devraient disposer dune nouvelle interface mémoire qui fera appel à la FB-DIMM (fully-buffered DIMMM) qui consiste à placer un intermédiaire entre les puces mémoire et le contrôleur. Cela permet de conserver des puces mémoires classiques avec un contrôleur très différent, lintermédiaire faisant en quelque sorte la conversion. Avec le FB-DIMM le connexion entre lintermédiaire et le contrôleur sera de type série, semblable au PCI Express, elle offrira des débits supérieurs et surtout permettra dutiliser plus de barrettes mémoire sur une même machine.Dual-core serveurLe fameux Montecito, Itanium dual-core de plus de 1.7 milliards de transistors devrait faire son apparition fin 2005. Il sera destiné aux serveurs équipé de 4 processeurs ou plus alors que le Milington sera la version destinées aux système bi-processeurs. Il disposera de quelques nouvelles technologies comme Pellston qui améliore la fiabilité du cache et Foxton qui permet un overclocking automatique de 10%.  Courant 2006 ces CPU seront remplacés par le Montvale qui devrait fonctionner à des fréquences plus élevées. Tous ces CPU seront fabriqués sur le process 90 nm, il faudra attendre le processeur Dinoma (DP) / Tukwila (MP) en 2007 pour lutilisation du process 65 nm. Notez au passage que ces Itanium devraient marquer la fusion de la plateforme Xeon avec la plateforme Itanium. Ils utiliseront la même interface électrique et le même socket et coûteront le même prix. Le Tukwila devait au départ intégrer au minimum 4 cores mais Intel aurait décidé de revoir ses plans et de rester à 2 cores mais plus performants. Toujours en 2007 le Poulson devrait prendre la relève du Tukwila avec plus de cores intégrés ? Vous remarquerez quIntel, même sil ne rentre pas dans les détails, indique clairement que de nombreux Itanium sont en cours de développement et réaffirme ainsi sa confiance dans larchitecture IA-64.  Le premier Xeon dual-core sera le Dempsey, équivalent au Presler, qui devrait voir le jour début 2006. Intel semble ainsi vouloir attendre le 65 nm et une enveloppe thermique revue à la baisse pour sattaquer au marché serveur avec le dual-core. Le Dempsey sera cependant limité au Dual Processor, et la version Multi (Quadri) Processor fera appel au core Paxville dérivé du core Smithfield. Les versions MP des CPU Intel ont généralement une génération de retard au niveau du process de fabrication, ce qui permet à Intel de faciliter leur développement. Néanmoins on peut se poser des questions sur le refroidissement qui sera nécessaire à un système équipé de 4 Paxville En 2007, au moment de la fusion des plateformes Xeon et Itanium, Intel devrait sortir le Whitefield, un CPU totalement différent des autres Xeon puisquil devrait être composé de 4 cores de Pentium M ! Page 8 - Dans le salon, Conclusion Intel dans votre salonComme tous les acteurs de lindustrie informatique, Intel a envie de conquérir votre salon. Cest un marché qui va évoluer très vite dans les années à venir, il est donc important pour un acteur comme Intel de se positionner au mieux sur ce marché et ce ne sera pas de tout repos. En effet, les premiers systèmes informatiques qui vont réellement conquérir en masse nos salons seront les consoles de prochaines générations. Et malheureusement pour Intel, aucune delles ne fait appel à un de leurs CPU, toutes se fourniront chez IBM. Intel devra se battre pour trouver sa place sur ce marché.    Intel a ainsi présenté et exposé plusieurs concepts de PC de salon réinventant presque le récent Mac Mini dApple. Pour la première fois, Intel a présenté une de ces machines équipée dune plateforme à base de Pentium M. Un virage important, le Pentium M hors du marché mobile nayant jamais été envisagé officiellement auparavant. Le Yonah devrait particulièrement bien y trouver sa place avec des capacités améliorées en traitement multimédia, le dual-core et une consommation réduite qui permet des formats compacts et des nuisances sonores réduites. Non content de vouloir investir nos salons, Intel vise également nos voitures. Les as du tuning de Pimp my Ride de MTV sont dailleurs venus présenter leur dernière création à Craig Barrett : une voiture complètement méconnaissable équipée en Centrino et dont la plupart des contrôles peuvent être pris en charge à distance via un PDA.    ConclusionCe dernier IDF a été loccasion pour Intel daffirmer son engagement vers le multi-cores en lieu et place de la course à la fréquence, un virage important qui a été entrepris il y a quelques mois et qui sapprête à se concrétiser. La route reste semée dembûches étant donné que peu dapplications grand public sont capables, aujourdhui, de réellement profiter du multi-core. Bien entendu, même si des gains de performances conséquents ne sont pas encore dactualité, le gain en confort dutilisation, lui, lest ! Le système sera plus réactif, plus efficace en multi-tâche et pourra profiter dun gain significatif en performances dans quelques applications spécifiques, ce qui est déjà très bien et suffisant pour justifier lintroduction rapide du dual-core, même sil nintéressera, au départ, quun public réduit.  Intel qui était à la traîne par rapport à AMD en 2004 au niveau de lefficacité et des performances de ses CPU compte bien reconquérir les utilisateurs avancés mais également placer plus de CPU dans chaque habitation grâce à des plateformes mieux adaptées à chaque marché. La réorganisation dIntel et le changement de CEO vont complètement dans le sens dune optimisation de lapproche du marché, mais comme vous avez pu le comprendre à travers cet article, Intel semble toujours tenir à sa longue tradition de R&D, ce qui laisse penser que lavenir devrait rester riche en nouveautés technologiques. Intel qui était à la traîne par rapport à AMD en 2004 au niveau de lefficacité et des performances de ses CPU compte bien reconquérir les utilisateurs avancés mais également placer plus de CPU dans chaque habitation grâce à des plateformes mieux adaptées à chaque marché. La réorganisation dIntel et le changement de CEO vont complètement dans le sens dune optimisation de lapproche du marché, mais comme vous avez pu le comprendre à travers cet article, Intel semble toujours tenir à sa longue tradition de R&D, ce qui laisse penser que lavenir devrait rester riche en nouveautés technologiques.Si ceci nest pas pour nous déplaire, il ne faut toutefois pas perdre de vue que de nombreuses technologies comme lEFI (remplaçant du bios attendu depuis longtemps), le VT ou encore le LT avaient déjà été largement abordées par Intel dans le cadre des précédents IDF et quon attend donc leur implémentations pratique. Quand seront exactement introduites ces nouvelles technologies ? LT va-t-elle amener des contraintes importantes pour lutilisateur final ? Quelles seront les spécifications exactes des prochains chipsets ? Il faudra encore patienter quelques mois pour que tout ceci séclaire.  Copyright © 1997-2025 HardWare.fr. Tous droits réservés. |