Les derniers contenus liés aux tags AFDS et Temash

AFDS: Moins de 3 et 2W pour les APU de 2013/14

AFDS: ARM Cortex A5 dans les futures APU AMD

AFDS: Moins de 3 et 2W pour les APU de 2013/14

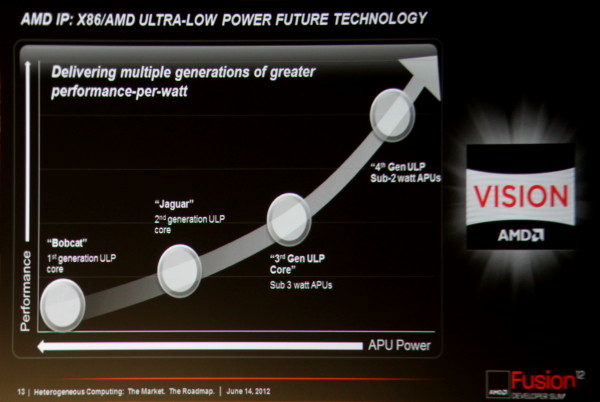

Sans dévoiler les traditionnels nouveaux noms de code qui accompagnent les roadmaps, AMD a présenté ses plans concernant les APU basse consommation qui succèderont à Brazos 2.0, basée sur les cores Bobcat, ainsi qu'à Temash basée sur les cores Jaguar.

Pour rappel, en 2013 c'est l'APU Temash qui sera chargée du marché des tablettes. Elle pourra embarquer jusqu'à 4 cores Jaguar (AMD parlait précédemment de 2 cores), un GPU dérivé de l'architecture GCN et sera proposée au format FT3 BGA avec un TDP variant entre 3.6W et 5.9W.

En 2013, une troisième génération de cores ultra basse consommation sera introduite avec pour objectif de pouvoir réduire la consommation totale de l'APU à moins de 3W, alors que la quatrième génération de cores aura pour objectif de faire passer l'APU sous les 2W en 2014. De quoi pouvoir proposer des composants plus intéressants pour les tablettes et enfin entrevoir une présence dans des smartphones ?

AFDS: ARM Cortex A5 dans les futures APU AMD

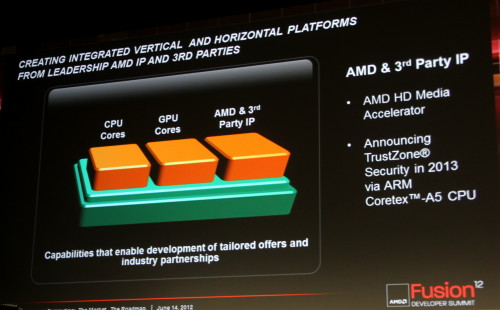

Il y a quelques mois, AMD avait expliqué être en train de réorganiser ses méthodes de développement pour atteindre un niveau de modularité similaire à celui des SoC. En plus de réduire les coûts à terme, une telle approche permet de gagner en flexibilité et de pouvoir intégrer plus facilement des technologies tierces à ses produits. AMD ayant précisé vaguement ne pas être forcément limité à l'ISA x86, la conclusion logique était que des cores ARM ou dérivés de son jeu d'instruction feraient leur apparition dans de futurs produits AMD.

C'est ce qui aura lieu dès l'an prochain, mais pas spécialement sous la forme que certains attendaient, telle qu'un SoC combinant cores ARM et GPU Radeon. Si un tel produit pourrait voir le jour dans le futur, ce n'est pas la première utilisation visée par l'utilisation de cores ARM. AMD souffre actuellement de l'absence de technologie de sécurisation dans ses plateformes, telle que la Trusted Execution Technology d'Intel (TXT), qui permet de sécuriser certains systèmes de paiement, DRM et autres infrastructures professionnelles et est vouée à se généraliser à l'avenir. Développer en interne une telle technologie est complexe et coûteux, d'autant plus qu'il faut ensuite convaincre tout l'écosystème de la supporter.

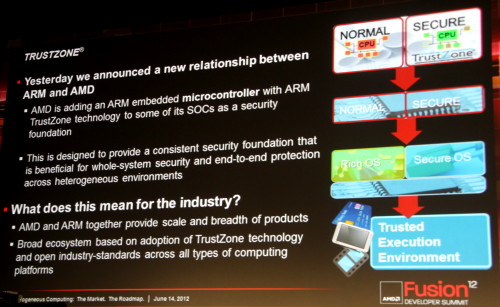

Malheureusement pour AMD, TXT ne fait pas partie de la licence x86 et l'accès à cette technologie n'est pas automatique. Intel ayant probablement rechigné à transférer sa technologie sous licence, ou le coût de cette celle-ci étant prohibitif, AMD a décidé de se tourner vers TrustZone d'ARM. Il s'agit de la plateforme concurrente principale de TXT et elle est présente au sein de tous les cores Cortex A. Elle repose sur une extension du jeu d'instruction d'ARM et ne peut donc pas être transposée facilement dans un core x86.

AMD a donc décidé d'inclure un core ARM dans ses futures APU, à commencer par Kabini et Temash qui succèderont à Brazos 2.0 et Hondo l'an prochain, avant de le généraliser à l'ensemble de ses produits. AMD a opté pour un Cortex A5, qui est le plus petit core de la famille : 0.53mm² en 40nm soit en principe moins de 0.30mm² en 28nm. Son intégration prendra probablement un petit peu plus de place mais à l'échelle de la puce elle aura un impact insignifiant.

AMD n'a pour l'instant pas donné plus de détails sur l'implémentation, ni sur la manière dont ce core ARM interagira avec les cores x86 dont il devra contrôler l'exécution, et encore moins sur l'exposition directe éventuelle de ce core qui pourrait par exemple être exploité par un antivirus. Une utilisation qui permettrait par exemple à AMD de répondre à l'intégration dans les CPU Intel d'optimisations destinées aux logiciels McAfee.