Les contenus liés au tag PCI Express 4.0

Le PCI Express 4.0, en retard, pour fin 2016

AVX3 et PCI Express 4.0 chez Intel

16 GT/s pour le PCI Express 4.0

Le PCI Express 4.0, en retard, pour fin 2016

![]() Lorsqu'il a été annoncé fin 2011, le PCI Express 4.0 devait être finalisé en 2014 ou 2015. Sur la FAQ dédiée à cette nouvelle norme , l'organisme PCI-SIG indique désormais que cela ne devrait être le cas que fin 2016. Ce changement semble dater du début d'année, il était question de fin 2015 auparavant, un changement datant de 2012 qui laissait déjà augurer d'un petit retard par rapport à ce qui était initialement prévu.

Lorsqu'il a été annoncé fin 2011, le PCI Express 4.0 devait être finalisé en 2014 ou 2015. Sur la FAQ dédiée à cette nouvelle norme , l'organisme PCI-SIG indique désormais que cela ne devrait être le cas que fin 2016. Ce changement semble dater du début d'année, il était question de fin 2015 auparavant, un changement datant de 2012 qui laissait déjà augurer d'un petit retard par rapport à ce qui était initialement prévu.

Pour rappel cette nouvelle version a pour but de doubler les débits par rapport au PCIe 3.0, avec 16 Gigatransferts par seconde ce qui avec le codage 128b/130b permet quasiment d'atteindre 2 Go /s par ligne dans chaque direction. En x16 on atteindrait donc 32 Go/s, contre 4 Go/s pour le désormais antique PCIe 1.0 qui a débarqué dans nos machines en 2004. Intel devait commencer à supporter le PCIe 4.0 à compter de Skylake-E qui devrait justement arriver autour de fin 2016 également, reste à voir si le retard dans les spécifications finales permettra à Intel de maintenir ce support.

AVX3 et PCI Express 4.0 chez Intel

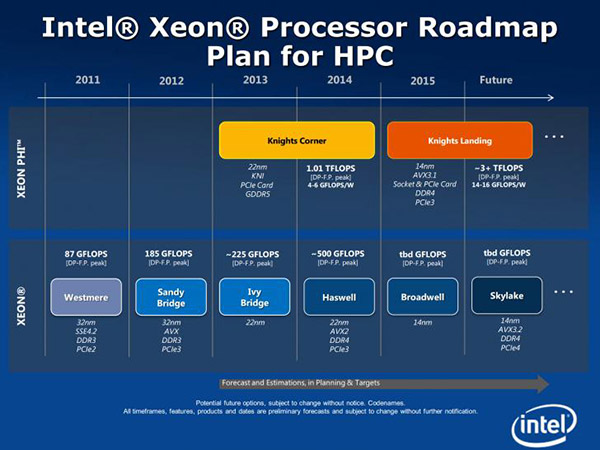

PC Games Hardware a trouvé un extrait de la roadmap Intel Xeon d'Intel apportant quelques (maigres) informations à l'horizon 2015 et au-delà.

Côté Xeon classiques tout d'abord, comme prévu on devrait voir débarquer en 2014 le Haswell, ou plus précisément les Haswell-E, EP et EN, qui apporteront leur lot de nouveautés avec notamment le support de l'AVX2, de la DDR4. L'AVX2 combiné à une augmentation du nombre de curs permettra à Intel de doubler le nombre de Gflops annoncé avec jusqu'à environ 500 Gflops.

Contrairement aux LGA 1150 la future plate-forme LGA2011-3 devrait a priori avoir droit au die shrink 14nm de Haswell, Broadwell, qui débarquera du coup en 2015 en version Xeon (il est prévu en 2014 en versions BGA, principalement pour les CPU Mobiles). Skylake arrivera dans un second temps, probablement en 2016 contre 2015 en version Core i7/i5 "classique". Sur la gamme Xeon il apportera entre autre le support de l'AVX3.2, dont on ne connait pas les nouveautés par rapport à l'AVX2, ainsi que du PCI Express 4.0 qui permettra de doubler la bande passante par rapport à la version 3 (soit 2 Go /s dans chaque sens par ligne).

On peut logiquement penser que l'AVX3.2 sera également intégré sur la déclinaison plus grand public de Skylake prévue pour 2015, pour le PCI Express 4.0 cela dépendra probablement de la date à laquelle la spécification finale sera publiée par le PCI-SIG. Pour le moment l'organisme n'est pas plus précis que 2014-2015 quand à cette publication. Cette déclinaison de Skylake devrait également intégrer le support de la DDR4, un an après son support sur les Xeon donc.

Sur la roadmap des Xeon Phi, les accélérateurs pour calculs parallèles dédiées au marché HPC d'Intel, on voit que les les Knights Landing devrait débarquer en 2015. Gravées en 14nm contre 22nm pour la génération actuelle, ils embarqueront un jeu d'instruction AVX3.1 et supporteront la DDR4 comme le PCI Express 3.0 pour une puissance et une efficacité énergétique qui seraient triplée par rapport aux versions actuelles. Intel parle de déclinaison sous forme de carte additionnelle, comme c'est le cas pour les Xeon Phi existantes, mais également de versions "Socket". On peut donc imaginer des cartes mères serveurs intégrant un Socket principal destiné au processeur Xeon classique, et un ou plusieurs Socket destinés à accueillir des Xeon Phi.

16 GT/s pour le PCI Express 4.0

![]() Alors que l'on attend encore les premiers périphériques au standard PCI Express 3.0, le comité de standardisation dédié au PCI Express, le PCI-SIG, vient d'annoncer le choix du bitrate de la version 4.0 du protocole. Il s'agira de 16 gigatransferts par seconde, le double de ce que permet le PCI Express 3.0 et ce qui représente en pratique 2 Go/secondes par ligne dans chaque direction.

Alors que l'on attend encore les premiers périphériques au standard PCI Express 3.0, le comité de standardisation dédié au PCI Express, le PCI-SIG, vient d'annoncer le choix du bitrate de la version 4.0 du protocole. Il s'agira de 16 gigatransferts par seconde, le double de ce que permet le PCI Express 3.0 et ce qui représente en pratique 2 Go/secondes par ligne dans chaque direction.

Le PCI-SIG annonce avoir effectué une étude de faisabilité pour vérifier si de tels débits pouvaient être déployés en gardant des pistes en cuivre sans augmenter la consommation électrique. L'étude a également vérifié qu'il serait possible de réaliser des interconnections en silicium capable de maintenir ces débits à bas cout, une condition importante pour le succès à terme de la technologie.

Si le but principal de la norme est de doubler le débit tout en maintenant la rétrocompatibilité, le comité espère pouvoir réaliser de nouvelles réductions de la consommation électrique, que ce soit en charge ou au repos. La version finale de la spécification n'est pas attendue avant 2014 à 2015, les produit devant arriver environ un an plus tard.