Les derniers contenus liés au tag Knights Corner

Intel dévoile l'AVX-512

Intel Xeon Phi, 50 coeurs x86 en PCIe

Intel présente Knights Corner et ses 50+ coeurs

''Larrabee'' 50 cores en 22nm chez Intel

Intel dévoile l'AVX-512

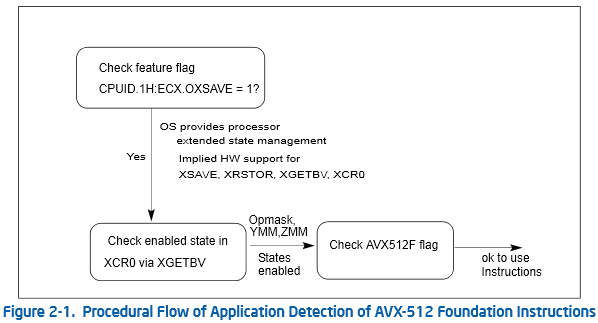

C'est par le biais d'un de ses blogs qu'Intel vient d'annoncer la prochaine version d'AVX, que l'on connaissait précédemment sous le nom de code 3.1 et 3.2. Il s'agira finalement d'AVX-512.

Comme son nom l'indique, AVX-512 est une extension du jeu d'instruction AVX qui rajoute des instructions SIMD (une instruction qui s'applique à de multiples données) 512 bits, soit le double de l'AVX actuel, pouvant cibler aussi bien des données entières que flottantes. Ce n'est pas la première fois que l'on voit un jeu d'instructions 512 bits chez Intel car c'est précisément ce que proposait le jeu d'instruction de Larrabee, et plus récemment de Knights Corner que l'on connait sous la dénomination commerciale Xeon Phi.

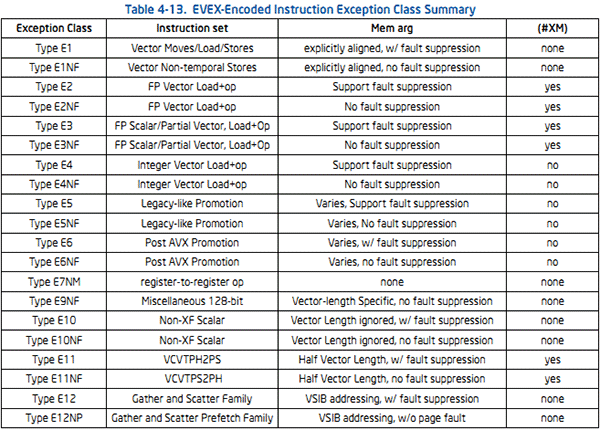

AVX-512 apporte une série de changements détaillés dans ce document PDF, on notera en premier lieu le nombre de registres qui passe de 16 à 32, tandis que les nouvelles instructions sont préfixées EVEX (au lieu de VEX pour AVX2). Ces dernières concernent aussi bien les entiers que les flottants et vous pourrez retrouver ci-dessous les grandes familles (classes) d'instructions disponibles.

La liste des classes d'instructions d'AVX-512. Vous retrouverez dans le PDF la liste complète des instructions à la page 75.

Notez qu'Intel parle dans son document "d'AVX-512 Foundation", sous entendant qu'il s'agit là du socle commun et que certains produits pourraient proposer des instructions supplémentaires. Ce n'est pas forcément surprenant puisque ces slides indiquaient que Knights Landing (la prochaine version de Xeon Phi) utiliserait AVX3.1, tandis que Skylake (la prochaine nouvelle architecture CPU d'Intel qui apparaitra après Broadwell en 14nm) utilisera AVX 3.2.

Il sera intéressant de voir ce qu'Intel fera exactement de ces unités AVX 512 bits dans le processeur Skylake. Le directeur du Visual and Parrallel Architecture Group d'Intel, Ofri Wechsler est en effet à la fois en charge des projets Xeon Phi du constructeur (l'actuel Knights Corner, le suivant Knights Landing, et le futur Knights Hill) mais aussi de l'architecture graphique qui sera utilisée dans Skylake.

Sa biographie sur le site d'Intel indique également qu'il était responsable du projet qui tentait de construire un pipeline de rendering 3D logiciel fonctionnant sur Larabee, l'ancêtre des actuels Xeon Phi. Si des rumeurs laissaient penser qu'Intel pourrait un jour utiliser ce type de solution pour remplacer un GPU, l'échéance de Skylake est probablement encore trop proche pour que l'on voit arriver ce type de solution pour remplacer l'iGPU intégré aux processeurs. Skylake dans sa version desktop est en effet prévu pour 2015.

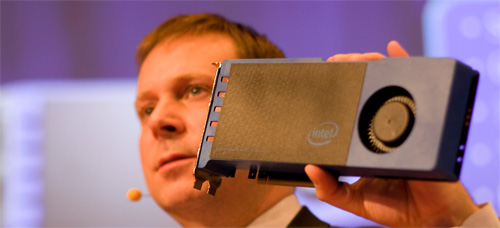

Intel Xeon Phi, 50 coeurs x86 en PCIe

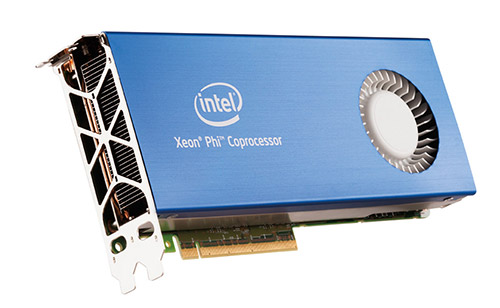

Intel profite de l'ISC (International Supercomputing Conference) pour annoncer une nouvelle marque, Xeon Phi, qui accueillera les produits dérivés de son architecture MIC (Many Integrated Cores). Le premier produit devrait être disponible fin 2012, il sera basé sur la puce au nom de code Knights Corner dont on entend parler depuis 2010, étant elle-même dérivée de l'arlésienne Larrabee dont il était question depuis... 2007 !

Ce coprocesseur Intel Xeon Phi intégrera plus de 50 curs x86 et leurs unités SIMD 512 bits gravés en 22nm Tri-Gate, et il prendra place sur une carte au format PCIe au côté d'un minimum de 8 Go de GDDR5. La performance annoncée de 1 TeraFLOPS sous DGEMM l'an passé a été confirmée à l'ICS sous Linpack (Rmax).

Intel met pour rappel en avant la flexibilité de son architecture, due à l'utilisation d'un cur x86 généraliste (dérivé d'un Pentium P54C) pour piloter son unité SIMD, même s'il faudra attendre de voir la qualité des outils en pratique.

L'université du Texas devrait mettre en ligne en 2013 le premier supercalculateur architecturé autour de Xeon Phi. Il sera basé sur des milliers de Xeon E5 8 curs et de Xeon Phi, fournissant des puissances de calcul respectives de 2 petaFLOPS et 8 petaFLOPS. Intel compte atteindre l'exaFLOPS pour un supercalculateur d'ici 2018, soit l'équivalent d'un millions des actuels Xeon Phi.

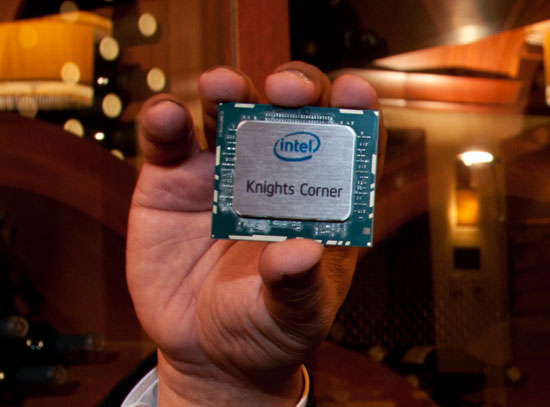

Intel présente Knights Corner et ses 50+ coeurs

C'est dans le cadre d'une conférence dédiée au High Performance Computing, la SC11 qui se tenait cette semaine à Seattle qu'Intel a effectué une première présentation de sa puce MIC (Many Integrated Cores) Knights Corner.

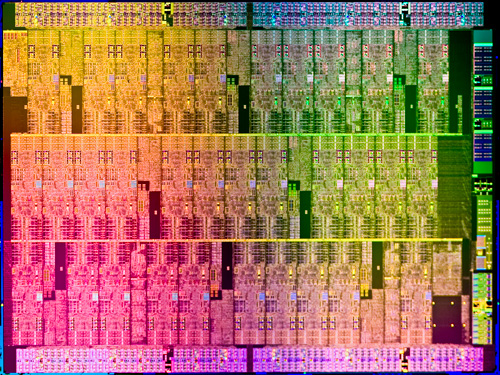

Il s'agit du descendant direct du projet Larrabee qui devait avoir le double emploi d'être un GPU et un accélérateur de calcul. L'architecture de Larrabee reposait sur de multiples curs (32) reliés par un ring bus et composés chacun d'une unité x86 à laquelle était accolée une unité SIMD 512 bits.

Knights Corner avait été annoncé il y a un peu plus d'un an de cela par Intel comme un processeur prévu pour 2012 et équipé de 50 curs et gravé en 22 nm (Tri-Gate, voir notre présentation). Le communiqué de presse d'Intel confirme ces caractéristiques, indiquant cependant qu'il s'agira de "plus de 50 curs" sans préciser combien.

Intel a annoncé un premier chiffre de performances d'au moins un TeraFlop pour Knights Corner, en calcul virgule flottante double précision sous DGEMM (multiplications de matrices présentes dans la bibliothèque BLAS, utilisée notoirement par LINPACK/LAPACK), soit quasiment plus du double des performances maximales théoriques - qui sont loin d'êtres atteintes en pratique - des GPU actuels (515 GFlops pour Fermi/GF110 en version Tesla, 676 pour Cayman). Intel mettant en avant en plus la flexibilité de son architecture, due à l'utilisation d'un cur x86 généraliste (dérivé d'un Pentium P54C) pour piloter son unité SIMD, même s'il faudra attendre de voir la qualité des outils en pratique.

Le die Aubrey Isle des premiers Larrabee

Quelques détails ont également été confirmés comme le fait que Knights Corner, à l'image de Larrabee en son temps, fonctionne comme un système indépendant de l'hôte en faisant tourner son propre système d'exploitation (un noyau Linux) qui peut ainsi être adressé comme un nud à part entière dans une architecture HPC (les "programmes" Larrabee utilisent un couple de deux exécutables séparés, un pour l'hôte, un pour la carte).

Si Intel a bel et bien confirmé que Knights Corner serait le premier produit commercial issu de son architecture MIC, la date de 2012 évoquée précédemment n'a pas été confirmée officiellement.

''Larrabee'' 50 cores en 22nm chez Intel

Intel vient d'annoncer son intention de délivrer des produits basés sur son architecture Many Integrated Core (MIC) afin de créer des plates-formes traitant des teraflops. Destiné au HPC (High Performance Computing), le premier produit, "Knights Corner", sera gravée en 22nm et devrait donc débarquer vers 2012. Doté de plus de 50 curs, ce processeur sera destiné à accélérer les calculs massivement parallèles.

Il s'agit en fait ni plus ni moins que d'une utilisation dans le cadre du HPC du projet Larrabee, abandonné en tant que puce graphique, ainsi que du CPU 48 cores SCC annoncé en décembre dernier. Intel livre d'ailleurs à l'heure actuelle les premiers kits de développement "Knights Ferry", qui prend côté hardware la forme d'une carte-fille PCI-Express qui embarque la puce Larrabee 1ère du nom (désormais nommée Aubrey Isle) qui est elle équipée de 32 cores à 1.2 GHz associés à un cache de 8 Mo et 1 à 2 Go de GDDR5.

Avec son architecture MIC, Intel tiens bien entendu à consolider sa place au sein du TOP 500 des supercalculateurs, 82% des systèmes étant équipé en Intel, notamment face à la poussée actuelle des GPU. On notera d'ailleurs que NVIDIA a fait une entrée remarquée à la 2nd place du TOP500 (1ère place théorique) de Juin avec un supercalculateur chinois architecturé autour de Tesla C2050 !