Les derniers contenus liés au tag Purley

Premiers Xeon + FPGA au prochain trimestre

Xeon Skylake pour 2017, 28 curs et 6 canaux

Premiers Xeon + FPGA au prochain trimestre

En 2014, Intel avait annoncé sa volonté de combiner un Xeon et une puce programmable FPGA. Si on attendait ces produits pour les Xeon "Purley" en Skylake prévus pour 2017 d'après cette roadmap, le fabricant a précisé qu'il livrerait les premières puces Xeon + FPGA dès le premier trimestre 2016 à des fournisseurs de services cloud afin qu'ils optimisent leur algorithmes pour tirer parti du FPGA.

Pour rappel, Intel a annoncé en juin dernier le rachat du spécialiste des FPGA Altera avec lequel il avait déjà un partenariat pour l'utilisation de ses usines. Xilinx, autre spécialiste du FPGA, a pour sa part annoncé ces dernières semaines des collaborations avec Qualcomm et IBM afin d'associer des FPGA avec les architectures Power et ARM. Chacun affute donc ses armes pour ce qui semble être une des voies qui sera utilisée pour augmenter la puissance des centres de données dans les années qui viennent !

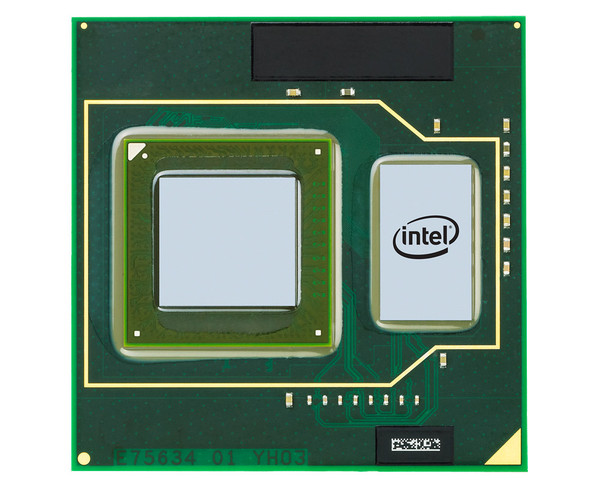

A noter qu'il ne s'agit pas d'une première pour Intel, qui avait déjà lancé en 2010 l'Atom E600C, qui combinait un Atom et un FPGA Altera (respectivement à droite et à gauche).

Xeon Skylake pour 2017, 28 curs et 6 canaux

On trouve sur ce lien une roadmap de la gamme Xeon d'Intel. Les plates-formes accueillant ou allant accueillir des Xeon E5/E7 v3 basés sur l'architecture Haswell verront débarquer en 2016 des Xeon v4 14nm de type "Broadwell". Ce sera en premier lieu le cas sur les E5-1600/2600 qui utilisent comme les Core i7 un LGA 2011-v3, plus tard dans l'année suivront les E7-8800/4800 v4 ainsi que les E5-4600 v4. Les Broadwell-EP correspondant aux E5 iront jusqu'à 22 curs et les Broadwell-EX (E7) jusqu'à 24, contre 18 pour les Haswell-EP et Haswell-EX.

Les déclinaisons Skylake ne sont pas attendues avant 2017, ce qui fera un décalage très important par rapport à l'apparition de cette architecture sur LGA 1151. Il faut dire qu'à cette occasion Intel va simplifier sa gamme Xeon avec seulement deux plates-formes : Basin Falls avec un mono Socket R (sur laquelle sera probablement basée celle des futurs i7 haut de gamme) et Purley qui ira de 2 à 8 sockets P. On passera cette fois à 28 curs au maximum et la mémoire DDR4 sera gérée sur 6 canaux, en mode 2666 avec 1 barrette par canal ou 2400 avec 2 barrettes.

Il n'est bizarrement pas fait mention du PCIe Gen4, par contre on passera à 48 lignes PCIe par processeur ce qui permet d'avoir 3 ports x16. Il est question d'un nouveau chipset Lewisburg qui intégrera un lien DMI3 avec le CPU et permettra de gérer jusqu'au 10 USB 3, 14 SATA 3 ou 20 PCIe, une partie des lignes étant probablement partagées. 4 ports Ethernet 10 GbE sont également gérés. Cette plate-forme supportera en sus l'Intel OmniPath 100G qui permet de disposer de liens optiques pour interconnecter les puces au sein d'un supercalculateur.

D'autres points sont plus flous, Intel met ainsi en avant une nouvelle architecture mémoire offrant à la fois une persistance de donnée, une vitesse 500 fois supérieure à la NAND, une capacité 4x supérieures ainsi qu'un coût inférieur à la DRAM. Intel met également en avant la possibilité de disposer d'accélérateurs spécifiques, tels que le QuickAssist pour le chiffrement et la décompression mais il est également question d'une association avec un FPGA (sous quelle forme ?) ainsi que de l'iGPU de Cannonlake. Nous aurons certainement des détails plus précis d'ici le lancement de Purley en 2017. Les futurs i7 haut de gamme seront pour leur part très probablement communs avec ceux de la plate-forme Basin Falls pour laquelle la présentation ne donne pas de détails.