L'Hybrid Memory Cube en production en 2014

Publié le 04/09/2013 à 17:40 par Guillaume Louel

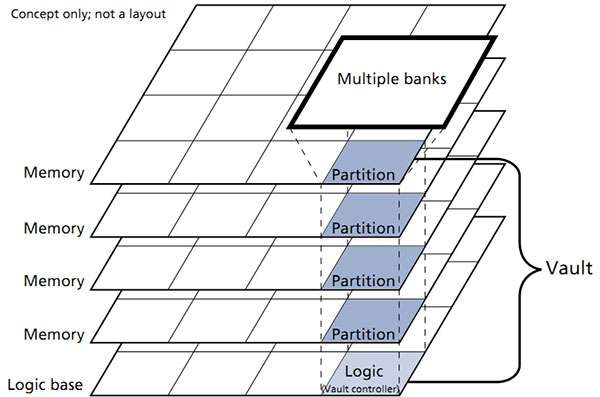

Nous vous avions parlé en 2011 du concept de l'Hybrid Memory Cube. Sur le papier il s'agit d'un concept simple, superposer une couche logique de contrôleurs mémoires avec de multiples dies de mémoire DRAM reliés les uns aux autres par des TSV (Through Silicon Vias, littéralement des fils qui passent au travers des différents dies, à l'opposée de la solution "classique" ou l'on fait passer les fils par le côté).

Chaque colonne sur le schéma représente un "vault" qui dispose en bas dans la couche logique de son propre contrôleur mémoire indépendant. L'avantage du système est d'être capable d'atteindre des bandes passantes très élevées, on parlait déjà en 2011 de 128 Go/s sur une seule puce !

Sur cet autre schéma, on peut voir le principe un peu plus en détail avec une puce qui superpose neuf dies (8 mémoires, un logique). On retrouve ici 16 vaults, chaque contrôleur est relié à un switch puis à quatre liens point à point vers l'extérieur de la puce. Ces nombres étant bien entendu modulables. Notez également que les cubes sont chainables entre eux.

Micron et d'autres sociétés (notamment ARM, HP, Hynix, IBM et Samsung) se sont alliés pour mettre en place un consortium dans le but de développer un standard commun. On notera avec un étonnement certain l'absence d'Intel dans ce consortium, alors que la société avait pourtant effectué les démonstrations lors de l'IDF 2011. La spécification (PDF) a été publiée en avril avec des débits très prometteurs allant de 160 à 240 Go/s pour les modèles à quatre liens (en fonction de la vitesse individuelle des liens), et 320 Go/s pour le modèle huit liens.

Micron avait indiqué en 2011 que c'est IBM qui produirait dans son process 32nm HKMG. Aujourd'hui, dans un communiqué qui parle de l'intérêt de l'intégration avec des FPGA, Micron s'engage un peu plus sur les dates en annonçant la livraison d'échantillons avant la fin de l'année, et surtout une production en volume pour 2014. On ne sait pas s'il s'agira toujours d'un process 32 HKMG. En déportant les contrôleurs mémoires directement dans les puces mémoires, l'Hybrid Memory Cube propose en plus d'un bond net de bande passante la possibilité de repenser les sous systèmes mémoires des processeurs. Reste à voir dans quel cadre elle pourra être utilisée. Le consortium indique viser très clairement les CPU et les GPU. Auprès de ces puces, l'HMC jouerait alors un rôle hybride à mi chemin entre ce que propose l'eDRAM et la mémoire traditionnelle.

Vos réactions

Contenus relatifs

- [+] 04/05: Cadence et Micron pour la DDR5-4400

- [+] 25/01: AMD annonce la restructuration de R...

- [+] 26/12: Micron a terminé la qualification d...

- [+] 24/11: Le prix de la RAM pousse les ventes...

- [+] 20/06: Micron cède à la mode du RGB pour l...

- [+] 07/06: Micron atteint 16 Gbps en GDDR5X, G...

- [+] 07/02: Micron : NAND 3D 64 couches pour ce...

- [+] 29/12: Les premiers portables avec Optane ...

- [+] 15/11: Des détails sur le 7nm à l'ISSCC 20...

- [+] 28/10: Nouveaux BIOS pour les GTX 1070 Mic...