Intel détaille son 22nm dédié aux SoC

Publié le 11/12/2012 à 11:57 par Guillaume Louel

A l'occasion de la conférence International Electron Devices Meeting qui se tient actuellement à San Francisco, Intel a donné quelques détails sur la version dédiée aux SoC de son procédé de fabrication 22nm. Des propos qui sont rapportés par nos confrères d'EETimes .

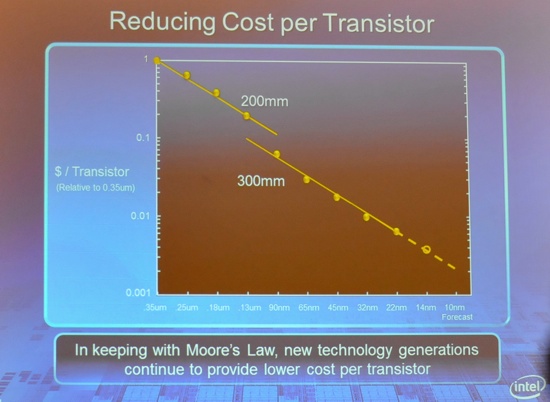

Evolution du cout des transistors, présenté par Intel lors de l'IDF en septembre dernier

Mark Bohr (que nous avions interviewé en septembre dernier durant l'IDF) en a profité pour répondre à quelques rumeurs sur le coût supposé du procédé de fabrication 22 nm d'Intel, indiquant que la technologie TriGate utilisée engendre un surcout de seulement 3% par rapport à un processus planaire équivalent.

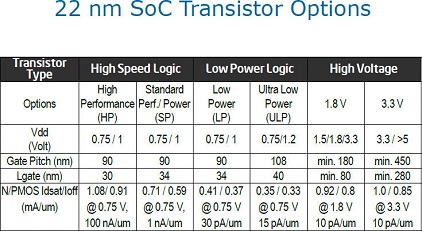

Les différents types de transistors 22nm SoC

Intel a annoncé avoir obtenu des gains de performances allant de 20 à 65% sur ses transistors SoC 22nm par rapport aux versions 32nm. L'autre différence, déjà évoquée lors de l'IDF concerne l'aspect flexible du process qui propose aux designers un large choix de transistors à utiliser. Des gains de 51 à 56% sur les transistors haute tension (utilisé pour les interfaces externes) sont mentionnés, tout comme un gain de performance significatif du côté des transistors analogiques.

L'arrivée des Atom SoC 22nm était pour rappel prévue pour 2013, même si les dernières rumeurs font état d'une arrivée pour 2014, tout du moins en déclinaison tablette.

Notons enfin que l'article de nos confrères mentionne également qu'IBM a également présenté ses travaux sur sa version du 22nm FinFet utilisant, surprise, des wafers de type PD-SOI. Lors de la conférence de la Common Platform (l'alliance qui regroupe IBM, Global Foundries et Samsung) en début d'année, l'utilisation du SOI pour le 22nm était un facteur de divergence entre les différents acteurs, Global Foundries ayant indiqué vouloir faire l'impasse pour ce node sur le SOI (après avoir déjà fait l'impasse pour le 28nm). IBM avait évoqué surtout à l'époque l'utilisation de SOI type Fully Depleted pour les process au-delà du 20nm.

Vos réactions

Contenus relatifs

- [+] 09/05: AMD Ryzen 7 2700, Ryzen 5 2600 et I...

- [+] 04/05: Un Coffee Lake 8 coeurs en préparat...

- [+] 27/04: Le 10nm d'Intel (encore) retardé, l...

- [+] 26/04: Jim Keller rejoint... Intel !

- [+] 19/04: 2008-2018 : tests de 62 processeurs...

- [+] 10/04: LGA4189 pour les Xeon Ice Lake !

- [+] 05/04: Pas de MAJ Microcode pour les Gulft...

- [+] 03/04: Intel lance la 2ème vague de sa 8èm...

- [+] 15/03: Microcode final pour Spectre chez I...

- [+] 08/03: GlobalFoundries : 12nm, 7nm et EUV