Actualités mémoires

Toshiba s'écarte un peu plus de WD

Samsung augmente la production de HBM2 8 Go

Arrêt d'une usine DRAM Micron, rumeur ou réalité ?

Toshiba passe à l'offensive contre WD

Toshiba a choisi le repreneur de sa mémoire

Le prix de la RAM pousse les ventes de Samsung

Comme nous vous l'indiquons régulièrement, les prix de la RAM n'ont cessé d'augmenter ces derniers mois. En septembre dernier, on pointait un doublement du prix en un an. Depuis les choses ne se sont pas arrangées avec une hausse en octobre, et encore en novembre.

Par rapport à notre relevé de septembre, les puces DDR4-2133 de 512 et 1Go ont augmenté 27.1 et 25% respectivement, atteignant aujourd'hui 4.795 et 9.595$. La DDR3 de son côté suit le mouvement, restant 10% moins chère sur les puces 512 Mo, un écart semblable a ceux que l'on a pu constater ces derniers mois.

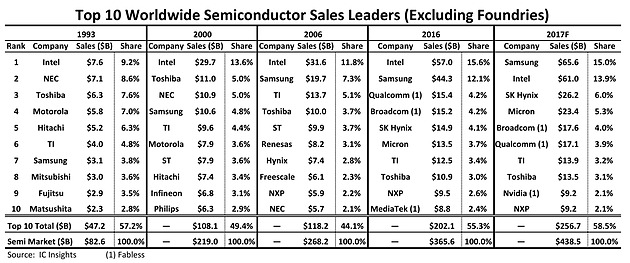

Au delà des conséquences très concrètes sur le prix des barrettes mémoires pour les utilisateurs de PC (en se rappelant qu'aujourd'hui, le PC compte pour une part limitée de la demande mondiale de mémoire), ces écarts favorisent largement les vendeurs de mémoire et de NAND comme Samsung qui, selon IC Insights devrait prendre la tête du classement des ventes de semi conducteurs pour l'année 2017, une place historiquement réservée à Intel !

Le classement d'IC Insights se base sur les ventes de semi conducteurs des sociétés en excluant les fabs comme TSMC et GlobalFoundries.

Ces chiffres sont préliminaires, l'année n'étant pas terminée, mais sur 2017, l'ensemble du marché des semi-conducteurs devrait progresser assez fortement, d'environ 20% par rapport à 2016.

Ce sont les acteurs de la RAM/NAND qui sont principalement derrière ces gains, et pas qu'un peu puisque l'on note des progressions de ventes de 48% pour Samsung, 75.8% pour SK Hynix et 73% pour Micron ! Ces deux dernières passent pour l'occasion devant Broadcom et Qualcomm. On notera enfin que Nvidia devrait rentrer dans le top 10 cette année au dépend de MediaTek.

La DDR4 toujours en hausse, pénurie à venir ?

Depuis notre dernière actualité mi-septembre, les prix de la mémoire n'ont pas cessé d'augmenter. Alors qu'ils avaient déjà doublé en un an, les prix de la DDR4 ont ainsi augmenté depuis de 13% et 17% pour les puces 1 Go et 512 Mo DDR4-2133/2400.

Une situation préoccupante qui reflète une demande très supérieure à l'offre sur le spot market de la mémoire d'après DRAMeXchange, marché qui permet d'acheter des puces au jour le jour au contraire des contrats d'approvisionnement à plus long terme pouvant être passés avec les fabricants. Résultat, plusieurs fabricants de barrettes mémoires ont stoppé la prise de commande ou ne livreront les commandées passées que dans un ou deux mois !

Voilà qui n'est pas de bon augure à l'approche des fêtes de fin d'année, souvent synonyme d'upgrade ou de nouvelle machine pour nombre d'entre nous...

Toshiba choisi Bain Capital pour ses mémoires

Le directoire de Toshiba vient finalement d'approuver la vente de l'intégralité de la division Toshiba Memory à K.K. Pangea, une société fondée par le consortium d'investisseurs dirigés par Bain Capital, pour environ 18 milliards de $. Le feuilleton n'est sans doute pas terminé puisque SanDisk, filiale de Western Digital qui était associée à Toshiba côté mémoire, va continuer de contester cette vente devant les juridictions compétentes.

On notera que si Toshiba ne donne pas d'autre nom que Bain Capital, SanDisk précise que SK Hynix fait partie du consortium alors que d'autres sources font également état d'Apple, Dell et Hoya Corporation.

Les prix de la DDR4 ont doublé en un an !

Depuis un an les prix de la mémoire n'ont cessé d'augmenter, si bien qu'avec la dernière hausse de 5% ces derniers jours les prix ont tout simplement doublé depuis le 14 septembre 2016 d'après les relevés de nos confrères de DRAMeXchange !

Alors qu'il fallait compter à l'époque 1.86$ et 3.72$ pour des puces DDR4-2133 de 512 Mo ou 1 Go, leur dernière cotation est ainsi de 3.77 et 7.65$. Une hausse qui se retrouve bien entendu intégralement dans les prix de vente, ainsi il devient de plus en plus dur de trouver 8 Go de DDR4 sous les 70 ... tarif auquel on pouvait acquérir 16 Go à l'époque, et ce malgré un taux de change /$ légèrement plus favorable.

Toshiba rejette une fois de plus Western Digital

MAJ : Bloomberg a confirmé qu'Apple avait bel et bien proposé d'investir 3 milliards dans l'offre de rachat portée par Bain Capital, qui inclut également Dell, SK Hynix, et... Seagate !

La situation s'envenime une fois de plus entre Toshiba et Western Digital. Le premier tente actuellement de revendre son activité mémoire (Toshiba Memory Corporation) pour couvrir des pertes importantes engendrées sur son activité nucléaire aux Etats-Unis.

Toshiba avait d'abord annoncé en juin avoir choisi un consortium porté par des investisseurs américains privés, Bain Capital, mais dont la majorité de l'offre était portée par SK Hynix en pratique. Quelque chose qui a fortement irrité Western Digital qui avait pour rappel racheté Sandisk (qui était historiquement lié à Toshiba via une Joint Venture).

Courant août, après quelques échanges juridiques, Toshiba avait annoncé investir, seul, dans sa future usine de mémoire.

Aujourd'hui la porte semble se refermer presque définitivement car Toshiba a annoncé, une seconde fois, avoir choisi l'offre de Bain Capital dans le but de négocier de manière définitive la cession de son activité, d'ici la fin du mois. Une discussion qui reste malgré tout... non-exclusive.

Trois offres étaient officiellement envisagées par la société japonaise, celle de Bain (a qui sont associées des fonds japonais pour des raisons politiques), celle de Western Digital et une troisième portée par Hon Hai. Le directoire de Toshiba aurait été séduit par une "nouvelle offre" de Bain.

La "nouvelle offre" est probablement liée à Apple qui, d'après nos confrères de Bloomberg , s'était associé d'une manière ou d'une autre à Bain Capital. Apple est pour rappel un très gros consommateur de mémoire NAND et tente régulièrement d'offrir un support financier aux constructeurs mémoire en payant a l'avance ses commandes. Un tel système pourrait être la nouveauté de l'offre d'après nos confrères, même si un investissement direct n'est pas exclu.

De son côté, Western Digital a annoncé sa déception en indiquant avoir été "flexible" et "constructif" avec son partenaire. Western Digital continue de marteler qu'en pratique l'offre est portée principalement par SK Hynix, quelque chose qui reste à vérifier dans le cas de la "nouvelle offre" pour laquelle nous n'avons pas plus de détails.